Project Number: EE-WZM-1B96

# DACS: The Distributed Audio Control System

A Major Qualifying Report submitted to the Faculty of the

## WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the  $\label{eq:Degree} \mbox{Degree of Bachelor of Science}$

by

Stephen Scott Richardson

Date: 25 July 1997

Approved

### Abstract

The Distributed Audio Control System (DACS) is a hybrid digital and analog system designed to automate common audio tasks such as audio mixing, digital audio cueing, and MIDI device control. The MQP explores the development of a powerful, expandible, and inexpensive system to perform these tasks. The implementation of two custom hardware components, firmware, and software bring the design to fruition, with near production quality.

# Acknowledgements

- Michael Andrews, for PCB proofing, ideas, and assistance with presentation.

- J. Nelson Chadderdon, for LCD backlight inverters and rail of LM1972's.

- Seann Ives, for selling me the HP logic analyzer.

- Professor William Michalson, for advising the project.

- Yeasah Pell, for loan of oscilloscope, laser printer use, random parts, loan of speakers for presentation.

- Mark and Paula Richardson, for funding the project.

- My suitemates, Yeasah and Dave, for putting up with the hardware lab in the living room and the testing/software lab in the bedroom.

- All of my friends (Kim, Sarah, Steph, Mike, Yeasah, Todd, and everyone else that I forgot) for their support throughout this project.

- WPI Lens and Lights, for the loan of a pair of EAW JF-60 speakers and tripods for the presentation.

# Contents

| 1        | Exe               | ecutive Summary 1                     | 12              |

|----------|-------------------|---------------------------------------|-----------------|

|          | 1.1               | What Does the System do?              | 12              |

|          | 1.2               | Why Design and Implement this System? | 12              |

|          | 1.3               | Project Goals                         | 12              |

|          | 1.4               |                                       | 12              |

|          | 1.5               | Conclusions                           | 13              |

| <b>2</b> | Tutu              | roduction                             | 14              |

| 4        | 2.1               |                                       | 14<br>14        |

|          | $\frac{2.1}{2.2}$ |                                       | $\frac{14}{15}$ |

|          | $\frac{2.2}{2.3}$ |                                       | 19<br>19        |

|          | 2.3               | System Overview                       | 19              |

| 3        | Hig               | ı                                     | 21              |

|          | 3.1               |                                       | 21              |

|          |                   | V                                     | 21              |

|          |                   | 1                                     | 22              |

|          |                   | v                                     | 23              |

|          |                   | 3.1.4 Concept Rendering               | 23              |

|          | 3.2               | Mixer Unit                            | 23              |

|          |                   | 3.2.1 System Description              | 23              |

|          |                   | 3.2.2 Specification Sheet             | 26              |

|          |                   | 3.2.3 Panel Layout                    | 29              |

|          |                   | 3.2.4 Concept Rendering               | 29              |

| 4        | Mod               | dule-Level Hardware Specifications    | 32              |

| -        | 4.1               | <u>-</u>                              | 32              |

|          |                   |                                       | 32              |

|          |                   |                                       | $\frac{32}{32}$ |

|          |                   |                                       | 34              |

|          |                   |                                       | 34              |

|          |                   | 1 0                                   | 34              |

|          |                   | ±                                     | 34              |

|          | 4.2               |                                       | 37              |

|          | 1.2               |                                       | 37              |

|          |                   | v i                                   | 37              |

|          |                   |                                       | 40              |

|          |                   | •                                     | 40              |

|          |                   |                                       | $40 \\ 41$      |

|          |                   |                                       | 41              |

|          |                   | <u> </u>                              | 41              |

|          |                   | 1                                     | $41 \\ 45$      |

|          |                   | 4.2.8 Microcontroller Module          | 40              |

| 5        | Inte              | er-Module Specifications              | <b>17</b>       |

|          | 5.1               | Control Board                         | 47              |

|          |                   | 5.1.1 Power                           | 47              |

|          | 5.2               | Mixer Unit                            | 47              |

|          |                   | 5.2.1 Gain Structure Diagram          | 47              |

|          |                   | 9                                     | 47              |

|          |                   | 5.2.3 Audio Signal Distribution       | 49              |

|          | 5.3               |                                       | 49              |

|          |                   |                                       | 51              |

|    |      | 5.3.2  | Timing and Levels                                 |   |     |

|----|------|--------|---------------------------------------------------|---|-----|

|    |      | 5.3.3  | Control Board I/O Map                             |   |     |

|    |      | 5.3.4  | Mixer Unit I/O Map                                |   |     |

|    |      | 5.3.5  | A/D Converter Connection                          |   |     |

|    |      | 5.3.6  | Control Board A/D Map                             |   | 55  |

| 6  | Har  | dware  | e Schematics                                      |   | 56  |

| •  | 6.1  |        | col Board                                         |   |     |

|    | 0.1  | 6.1.1  | Fader Module                                      |   |     |

|    |      | 6.1.2  | Output Assign Module                              |   |     |

|    |      | 6.1.3  | Transport Control Module                          |   |     |

|    |      | 6.1.4  | Universal User Interface and Cue Stack Submodules |   |     |

|    |      | 6.1.5  | Microcontroller Module (Pbus and LCD interfaces)  |   |     |

|    |      | 6.1.6  | Power Supply                                      |   |     |

|    | 6.2  | Mixer  |                                                   |   |     |

|    | 0.2  | 6.2.1  | Audio Input Module                                |   |     |

|    |      |        | <u>-</u>                                          |   |     |

|    |      | 6.2.2  | Audio Mix Module                                  |   |     |

|    |      | 6.2.3  | Bus Combiner and Switcher Module                  |   |     |

|    |      | 6.2.4  | Digital VU Module                                 |   |     |

|    |      | 6.2.5  | Audio Output Module                               |   |     |

|    |      | 6.2.6  | Microcontroller Module (Pbus and LCD interfaces)  |   |     |

|    |      | 6.2.7  | Power Supply                                      |   | 85  |

| 7  | Har  | dware  | e Verification                                    |   | 90  |

|    | 7.1  | Contro | rol Board                                         |   | 90  |

|    | 7.2  | Mixer  | : Unit                                            |   | 90  |

|    |      | 7.2.1  | Balanced Audio Input Module                       |   | 90  |

|    |      | 7.2.2  | Unbalanced Audio Input                            |   |     |

|    |      | 7.2.3  | Balanced Audio Output Module                      |   |     |

|    |      | 7.2.4  | Overall Noise Analysis                            |   |     |

|    |      | 7.2.5  | Total Harmonic Distortion Analysis                |   |     |

|    |      | 1.2.0  | Total Harmonic Distortion Amarysis                |   | 91  |

| 8  |      |        | e PC Board Designs                                |   | 92  |

|    | 8.1  |        | rol Board                                         |   |     |

|    |      | 8.1.1  | Fader Module                                      |   |     |

|    |      | 8.1.2  | Output Assign Module                              |   |     |

|    |      | 8.1.3  | Transport Control Module                          |   | 92  |

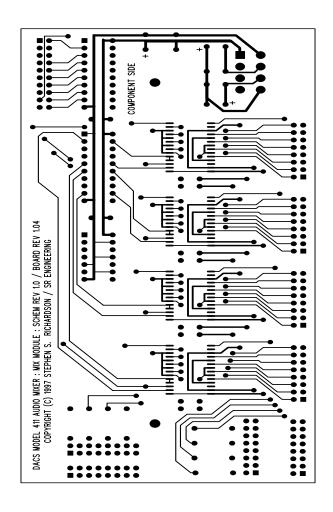

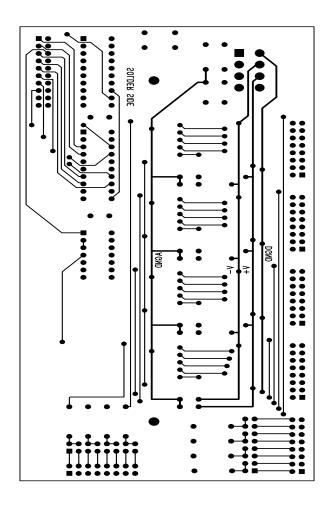

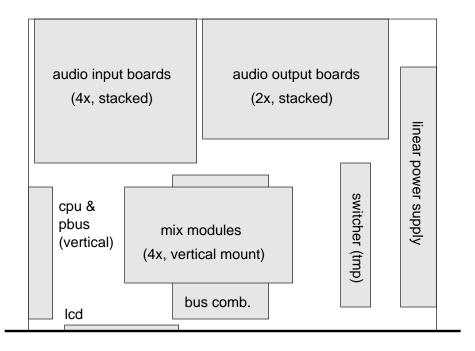

|    | 8.2  | Mixer  | : Unit                                            |   | 103 |

|    |      | 8.2.1  | Audio Input Module                                |   | 103 |

|    |      | 8.2.2  | Audio Mix Module                                  |   | 103 |

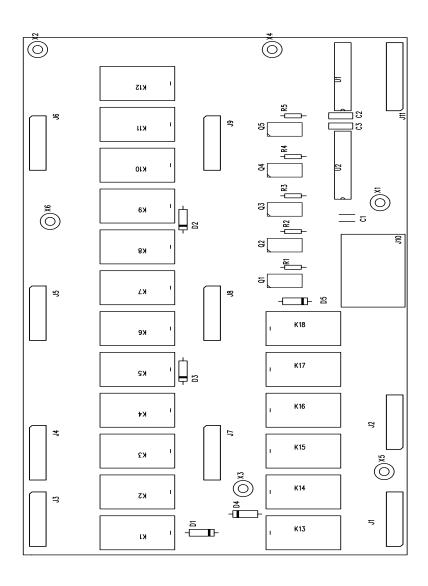

|    |      | 8.2.3  | Bus Combiner and Switcher Module                  |   | 110 |

|    |      | 8.2.4  | Audio Output Module                               |   | 110 |

| 0  | TT   | 1      | Ch:-                                              |   | 117 |

| 9  |      |        | e Chassis                                         |   | 117 |

|    | 9.1  |        | rol Board                                         |   |     |

|    | 9.2  | Mixer  | Unit                                              |   | 117 |

| 10 | High | h-Leve | el Firmware Design                                |   | 119 |

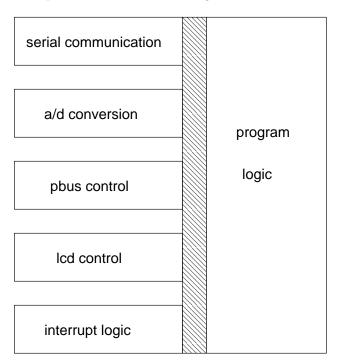

|    | _    |        | rol Board                                         |   | 119 |

|    |      | 10.1.1 | Design Overview                                   |   | 119 |

|    |      |        | 2 Overall Functional Design                       |   |     |

|    |      |        | Component Functional Design                       |   |     |

|    | 10.2 |        | Unit                                              |   |     |

|    |      |        |                                                   | - | _   |

|            |       | 10.2.1   | Design Overview                                    | <br>  | <br>    |     |   | 121          |

|------------|-------|----------|----------------------------------------------------|-------|---------|-----|---|--------------|

|            |       | 10.2.2   | Overall Functional Design                          | <br>  | <br>    |     |   | 123          |

|            |       | 10.2.3   | Component Functional Design                        | <br>  | <br>    |     |   | 124          |

|            | 10.3  |          | ACS Firmware Library                               |       |         |     |   | 125          |

|            |       |          | J. J           |       |         |     |   |              |

| 11         | Firn  | nware    | Protocols                                          |       |         |     |   | 127          |

|            | 11.1  | Serial   | Communications Protocol                            | <br>  | <br>    |     |   | 127          |

|            |       |          | Physical Layer                                     |       |         |     |   | 127          |

|            |       |          | Framing                                            |       |         |     |   | 127          |

|            |       |          | 21000000                                           | <br>  | <br>    |     |   |              |

| 12         | Firn  | nware    | Modules                                            |       |         |     |   | 129          |

|            | 12.1  | Firmw    | are Library                                        | <br>  | <br>    |     |   | 129          |

|            |       |          | ol Board                                           |       |         |     |   | 129          |

|            |       |          | Unit                                               |       |         |     |   | 130          |

|            | 12.0  | 1/11/101 |                                                    | <br>• | <br>• • | • • | • | 100          |

| 13         | Firn  | nware    | Code                                               |       |         |     |   | 132          |

|            | 13.1  | Firmw    | are Library, dacslib                               | <br>  | <br>    |     |   | 132          |

|            | 10.1  |          | SCI Serial Driver Header, SCIserial.h              |       |         |     |   | 132          |

|            |       |          | SCI Serial Driver Code, SCIserial.c                |       |         |     |   | 133          |

|            |       |          | ACIA Serial Driver Header File, ACIAserial.h       |       |         |     |   | 138          |

|            |       |          | ACIA Serial Driver Code, ACIAserial.c              |       |         |     |   | 140          |

|            |       |          |                                                    |       |         |     |   |              |

|            |       |          | Phus Driver Header File, phus.h                    |       |         |     |   | 145          |

|            |       |          | Pbus Driver Code, pbus.c                           |       |         |     |   | 146          |

|            |       |          | Pbus Defines Template, pbusdefn-template.h         |       |         |     |   | 147          |

|            |       |          | Alphanumeric LCD Driver Header, stdlcd.h           |       |         |     |   | 148          |

|            |       |          | Alphanumeric LCD Driver Code, stdlcd.c             |       |         |     |   | 149          |

|            | 13.2  | Contro   | ol Board                                           | <br>  | <br>    |     |   | 151          |

|            |       |          | Firmware Build, Makefile                           |       |         |     |   | 151          |

|            |       | 13.2.2   | Control Board Main Code, boardmain.c               | <br>  | <br>    |     |   | 152          |

|            |       | 13.2.3   | Interrupt Vector Table, boardvect.c                | <br>  | <br>    |     |   | 155          |

|            |       | 13.2.4   | Graphics LCD Driver Header, gfxlcd.h               | <br>  | <br>    |     |   | 155          |

|            |       |          | Graphics LCD Driver Code, gfxlcd.c                 |       |         |     |   | 156          |

|            |       |          | Alphanumeric and Graphics LCD Driver Defines, 1cdd |       |         |     |   | 159          |

|            |       |          | Pbus Driver Defines, pbusdefn.h                    |       |         |     |   | 160          |

|            | 13.3  |          | Unit                                               |       |         |     |   | 161          |

|            | 10.0  |          | Firmware Build, Makefile                           |       |         |     |   | 161          |

|            |       |          | Mixer Unit Main Code, mixmain.c                    |       |         |     |   | 162          |

|            |       |          | Interrupt Vector Table, mixwect.c                  |       |         |     |   | 166          |

|            |       |          | Mixer Driver Header, mixdrv.h                      |       |         |     |   | 166          |

|            |       |          |                                                    |       |         |     |   |              |

|            |       |          | Mixer Driver Code, mixdrv.c                        |       |         |     |   | 168          |

|            |       |          | Pbus Driver Defines, pbusdefn.h                    |       |         |     |   | 172          |

|            |       | 13.3.7   | Alphanumeric LCD Driver Defines, lcddefn.h         | <br>  | <br>    |     | • | 173          |

| - 1        | TT' ' | т.       |                                                    |       |         |     |   | 1 <b>=</b> = |

| 14         |       |          | l Software Design                                  |       |         |     |   | 175          |

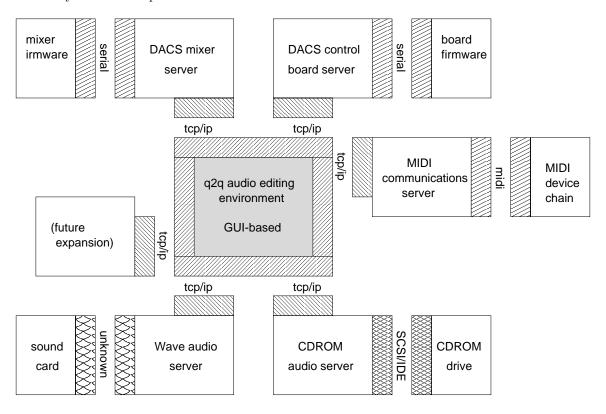

|            |       |          | ll System: The Distributed Concept                 |       |         |     |   | 175          |

|            | 14.2  |          | onal Design                                        |       |         |     |   | 176          |

|            |       |          | Service Providers                                  |       |         |     |   | 176          |

|            |       | 14.2.2   | Main Application                                   | <br>  | <br>    |     |   | 177          |

| <b>1</b> - | C     | _        |                                                    |       |         |     |   | 1 = 0        |

| Lb         | SOTT  | ware (   | Graphical User Interface                           |       |         |     |   | 179          |

| 16           | Soft | sware Code                                                          | 181 |

|--------------|------|---------------------------------------------------------------------|-----|

|              | 16.1 | MIDI Controller                                                     | 181 |

|              |      | 16.1.1 Main Program Code, midictrl.c                                | 181 |

|              |      | 16.1.2 MIDI Handler Header, midi.h                                  | 185 |

|              |      | 16.1.3 MIDI Handler Code, midi.c                                    | 187 |

|              |      | 16.1.4 Mixer Mid-Level Driver Header, mixer.h                       | 192 |

|              |      | 16.1.5 Mixer Mid-Level Driver Code, mixer.c                         | 192 |

|              |      | 16.1.6 CDROM Service Provider Communications Header, cdaudio_comm.h | 195 |

|              |      | 16.1.7 CDROM Service Provider CD Function Header, cdaudio_func.h    | 196 |

|              |      | 16.1.8 CDROM Service Provider Main Code, cdaudio_daemon.c           | 196 |

|              |      | 16.1.9 CDROM Service Provider CD Function Code, cdaudio_func.c      | 201 |

|              |      | 16.1.10 Serial Communications Header, serial.h                      | 205 |

|              |      | 16.1.11 Serial Communications Code, serial.c                        | 206 |

|              |      | 16.1.12 TCP/IP Client Library Header, client.h                      | 211 |

|              |      | 16.1.13 TCP/IP Client Library Code, client.c                        | 211 |

|              |      | 16.1.14 TCP/IP Server Library Header, server.h                      | 215 |

|              |      | 16.1.15 TCP/IP Server Library Code, server.c                        | 216 |

| $\mathbf{A}$ | VH   | DL Code                                                             | 220 |

|              | A.1  | Control Board                                                       | 220 |

|              |      | A.1.1 Fader Module                                                  | 220 |

|              |      | A.1.2 Output Assign Module                                          | 222 |

|              |      | A.1.3 Transport Control Module                                      | 225 |

|              | A.2  | Mixer Unit                                                          | 228 |

|              |      | A.2.1 Audio Input Module                                            | 228 |

|              |      | A.2.2 Mix Module                                                    | 230 |

|              |      | A.2.3 Bus Combiner Module                                           | 231 |

| В            | Axio | om MC68HC11 Single Board Computer References                        | 234 |

| $\mathbf{C}$ | Refe | erences                                                             | 239 |

|              |      | Books                                                               | 239 |

|              | C.2  | Data Books and Data Sheets                                          | 239 |

|              |      | Wab Sites                                                           | 230 |

# List of Figures

| 1               | Typical DACS-based home studio configuration                                                   | 15              |

|-----------------|------------------------------------------------------------------------------------------------|-----------------|

| 2               | Typical DACS-based broadcast application.                                                      | 16              |

| 3               | Typical DACS-based theatre audio application.                                                  | 17              |

| 4               | Typical DACS-based live sound application.                                                     | 18              |

| 5               | DACS component hierarchy, generalized view.                                                    | 20              |

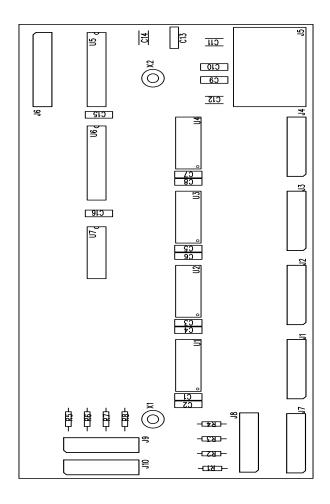

| 6               | Control board, panel layout and silkscreen artwork.                                            | 24              |

| 7               | Control board concept rendering.                                                               | 25              |

| 8               | Mixer unit panel layout and silkscreen artwork.                                                | 30              |

| 9               | Mixer unit concept rendering.                                                                  | 31              |

| 10              | Control board, overall system diagram.                                                         | 32              |

| 11              | Control board, module-level system diagram.                                                    | 33              |

| 12              | Control board, fader module diagram.                                                           | 34              |

| 13              | Control board, output assignment module diagram.                                               | 35              |

| 14              | Control board, transport module diagram.                                                       | 36              |

| 15              | Axiom CMM-11A8 single-board computer, used in the mixer unit                                   | 36              |

| 16              | Mixer unit, overall system diagram.                                                            | 37              |

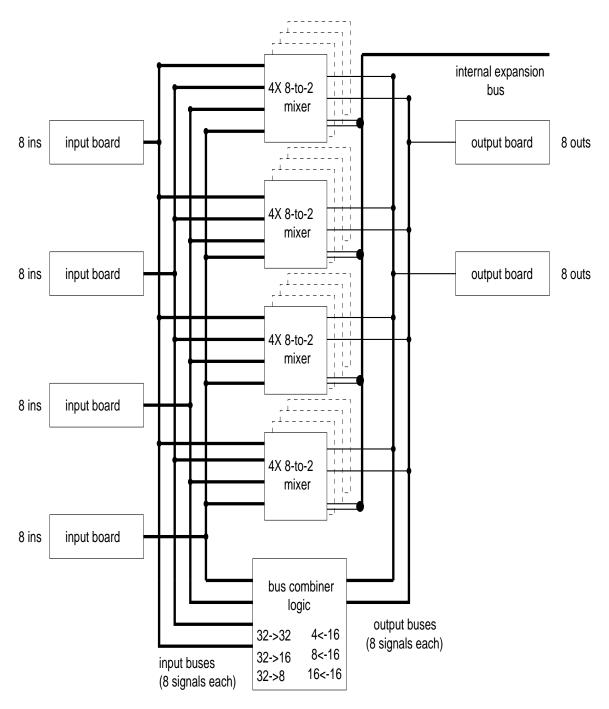

| 17              | Mixer unit, module-level system diagram (analog)                                               | 38              |

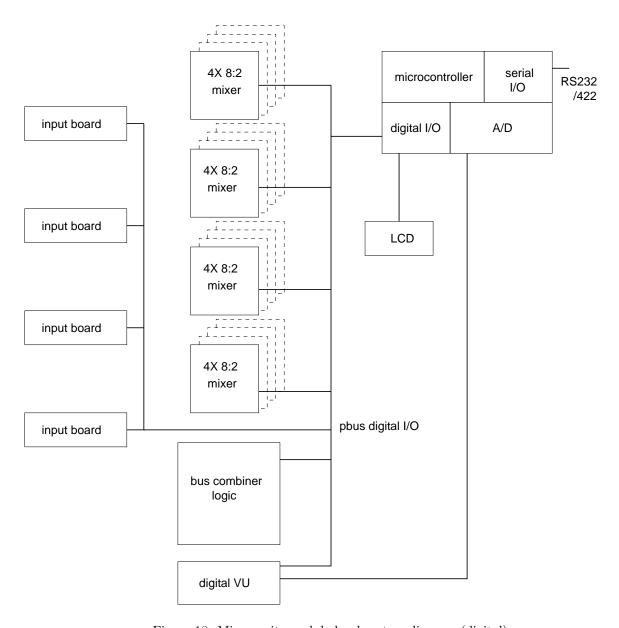

| 18              | Mixer unit, module-level system diagram (digital)                                              | 39              |

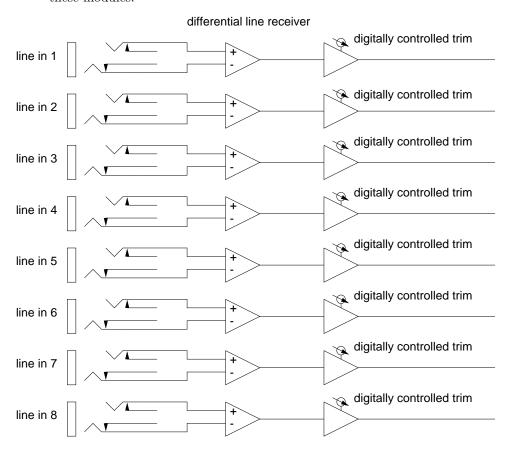

| 19              | Mixer unit, audio input module diagram.                                                        | 40              |

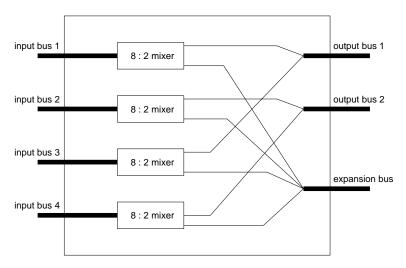

| 20              | Mixer unit, audio mix module diagram. Systems shall have four, eight or sixteen                | 40              |

| 20              | of these modules.                                                                              | 41              |

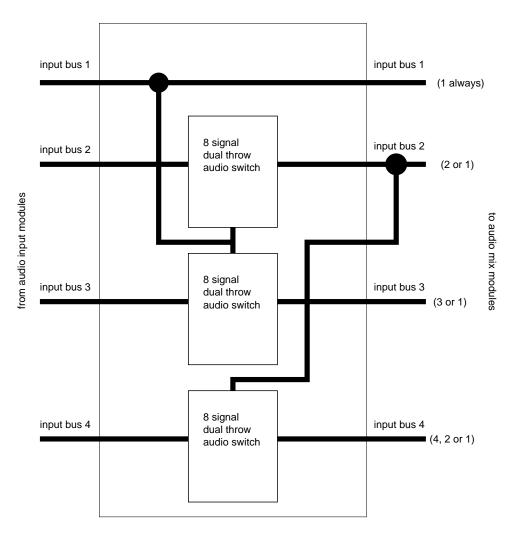

| 21              | Mixer unit, bus combiner module diagram (input buses).                                         | 41              |

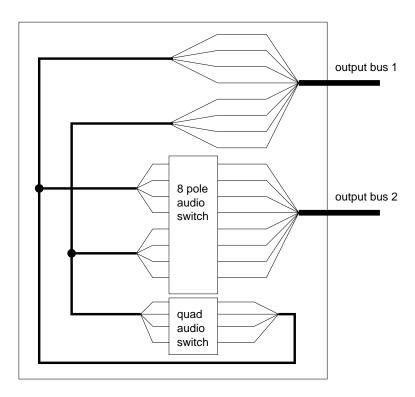

| $\frac{21}{22}$ | Mixer unit, bus combiner module diagram (output buses)                                         | 43              |

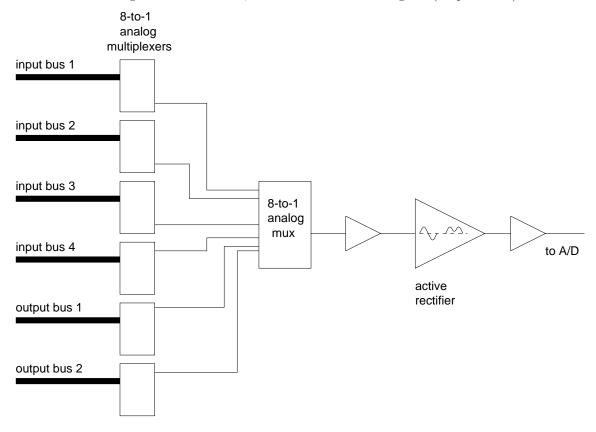

| 23              | Mixer unit, digital VU module diagram.                                                         | $\frac{43}{43}$ |

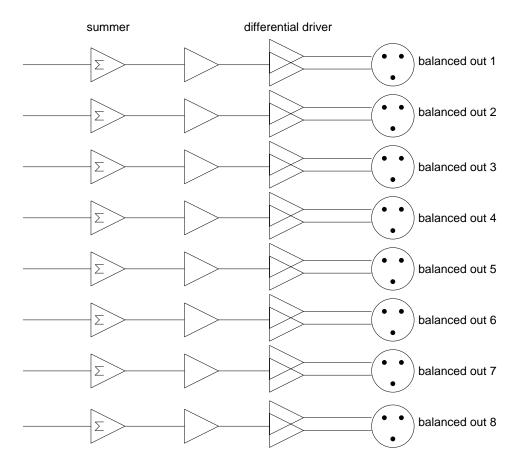

| $\frac{23}{24}$ | Mixer unit, digital vo module diagram                                                          |                 |

| $\frac{24}{25}$ |                                                                                                | 44              |

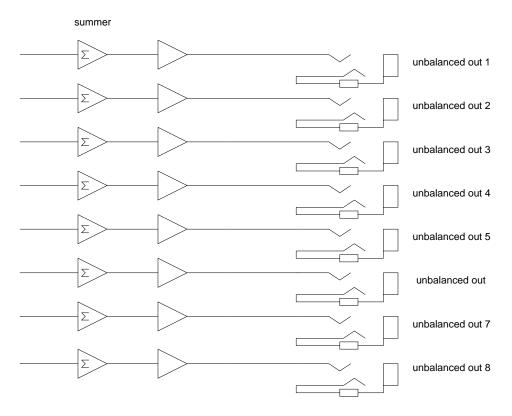

|                 | Mixer unit, unbalanced audio output module diagram.                                            | 45              |

| 26              | Axiom CMD-11A8 single-board computer, used in the mixer unit.                                  | 46              |

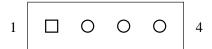

| 27              | 4 circuit 0.156in spaced connector, used for power distribution in the control board.          | 47              |

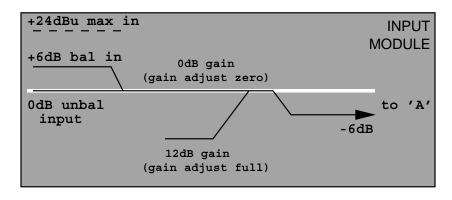

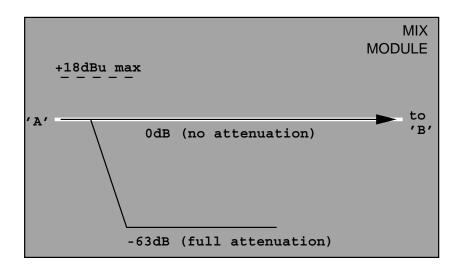

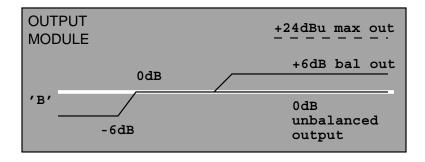

| 28              | Mixer unit gain structure diagram, input section.                                              | 48              |

| 29              | Mixer unit gain structure diagram, mixer section.                                              | 48              |

| 30              | Mixer unit gain structure diagram, output section.                                             | 48              |

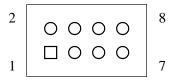

| 31              | 8 circuit <b>Molex</b> <i>Mini-Fit Jr.</i> connector, used for power distribution in the mixer | 4.0             |

| 00              | unit.                                                                                          | 49              |

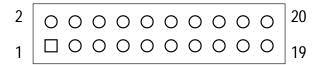

| 32              | Audio input bus pinouts. The 32 audio inputs are carried on four 16-pin headers.               |                 |

| 0.0             | † GND is <i>only</i> connected at the bus combiner board.                                      | 50              |

| 33              | Audio output bus pinouts. The 16 audio outputs are carried on two 16-pin headers.              | ٠.,             |

| 0.4             | † GND is <i>only</i> connected at the bus combiner board.                                      | 51              |

| 34              | DACS Pbus, physical description. A standard 0.100 inch DIP header of 20 pins                   |                 |

|                 | shall be used to connect each PC board to the bus. The bus itself shall be carried             |                 |

|                 | on 20 conductor ribbon cable, with each PC board connection made via a 20                      |                 |

|                 | conductor IDC. All signals are standard TTL levels                                             | 52              |

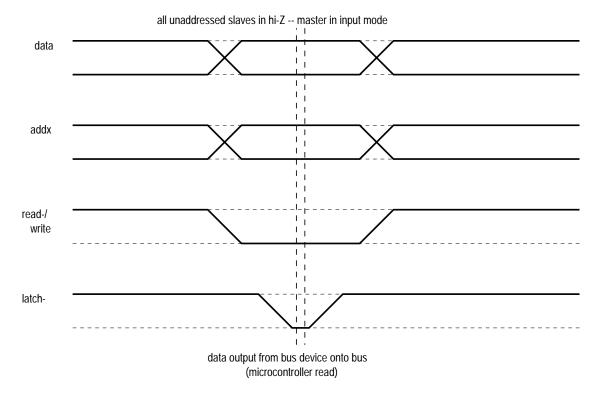

| 35              | Pbus timing diagram for input (Pbus master reading slave)                                      | 53              |

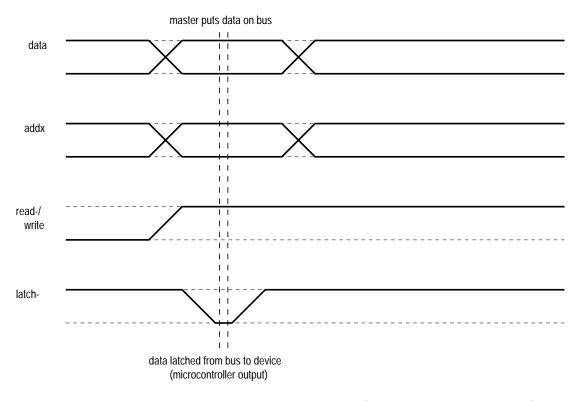

| 36              | Pbus timing diagram for output (Pbus master writing to slave)                                  | 53              |

| 37              | DACS control board prototype Pbus I/O map                                                      | 54              |

| 38              | Mixer unit Pbus I/O map.                                                                       | 54              |

| 39              | Analog-to-digital converter connector pinouts.                                                 | 54              |

| 40              | DACS board prototype A/D connector assignments                                                 | 55              |

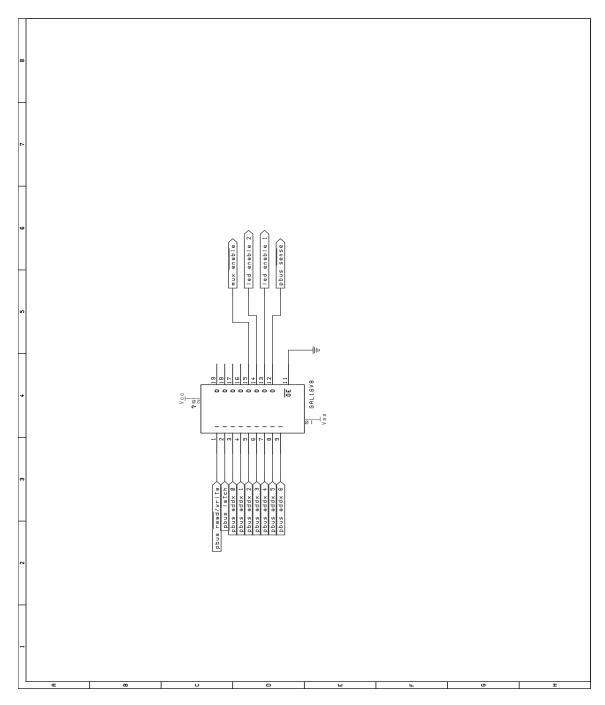

| 41              | Fader module, address decoding GAL pin layout.                                                 | 57              |

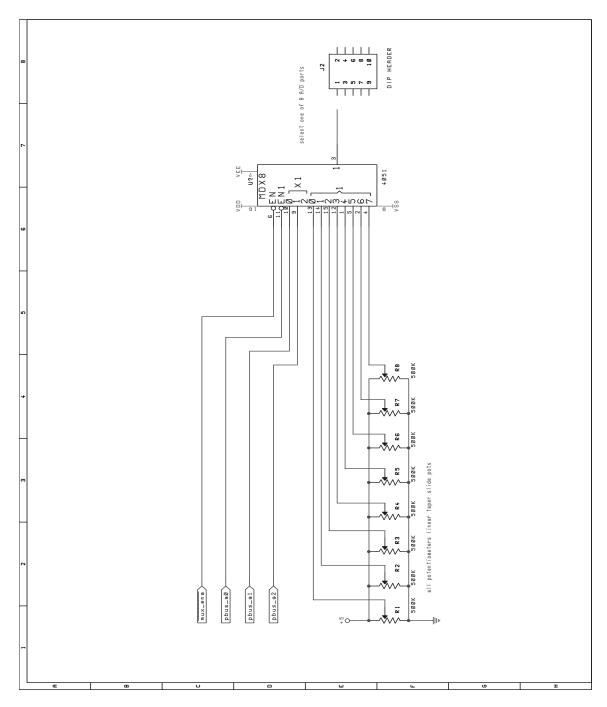

| 42              | Fader module, analog multiplexer circuit for potentiometers                                    | 58              |

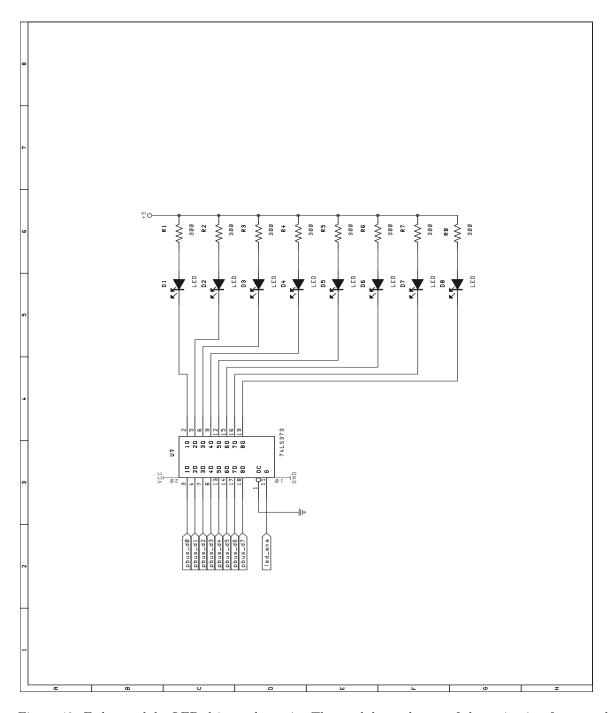

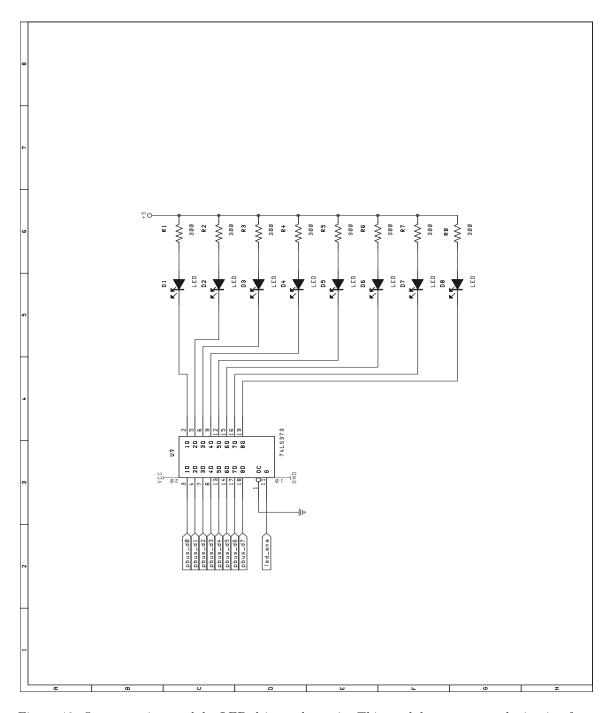

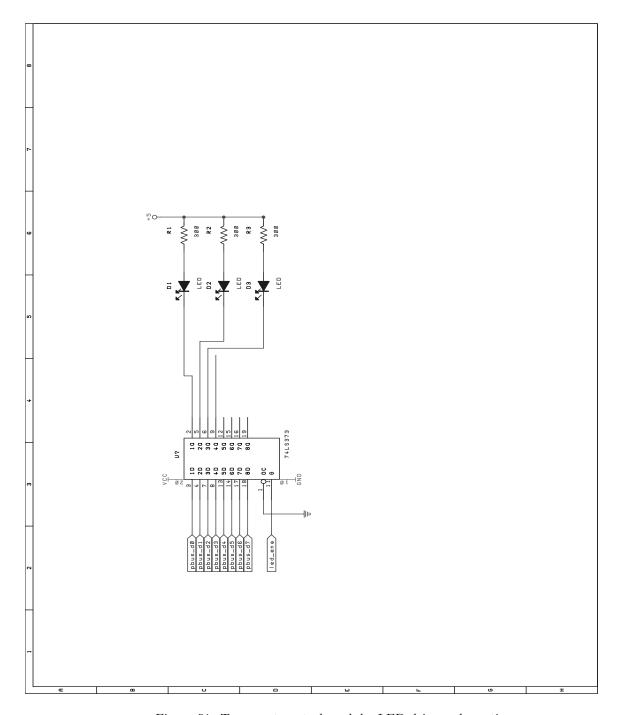

| 43              | Fader module, LED driver schematic. The module needs two of these circuits, for                |                 |

|                 | a total of 16 LEDs                                                                             | 59              |

| 44       | Output assign module, address decoding GAL 60                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

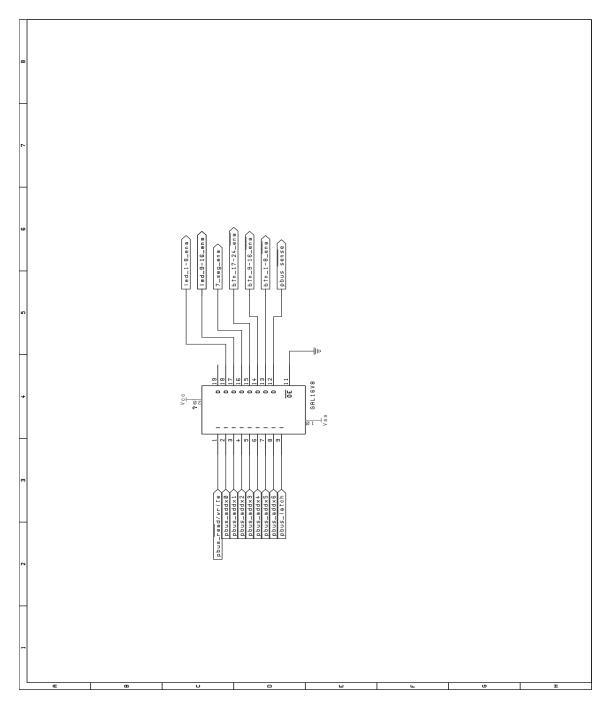

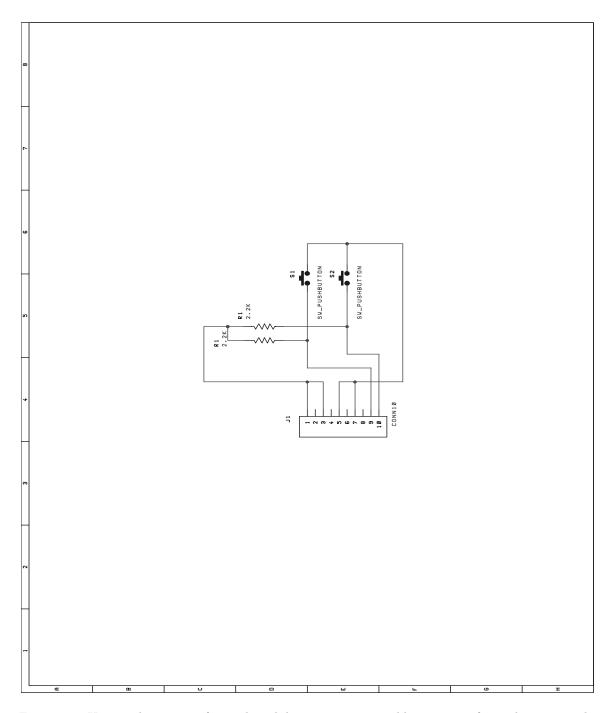

| 45       | Output assign module, momentary pushbutton decoding schematic. The output assign module uses three of these circuits, for a total decoding capability of 18 |

|          | on-board and 6 off-board buttons                                                                                                                            |

| 46       | Output assign module, LED driver schematic. This module uses two such circuits,                                                                             |

|          | for a total of 16 LEDs                                                                                                                                      |

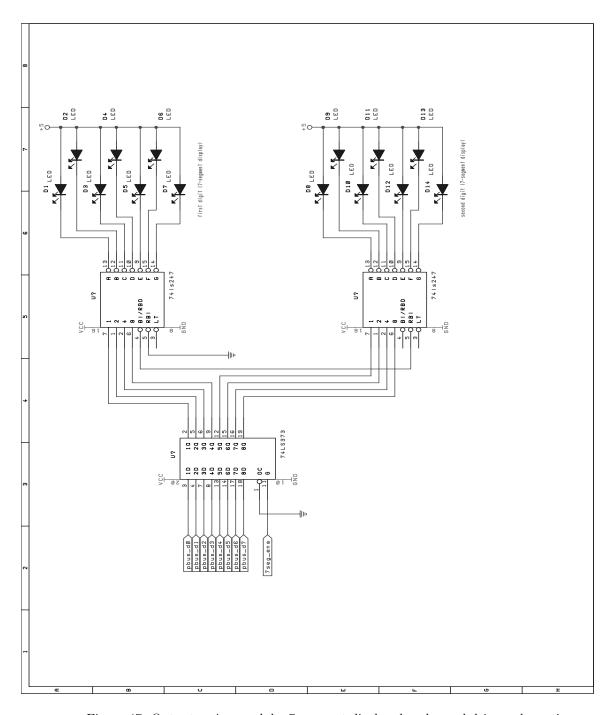

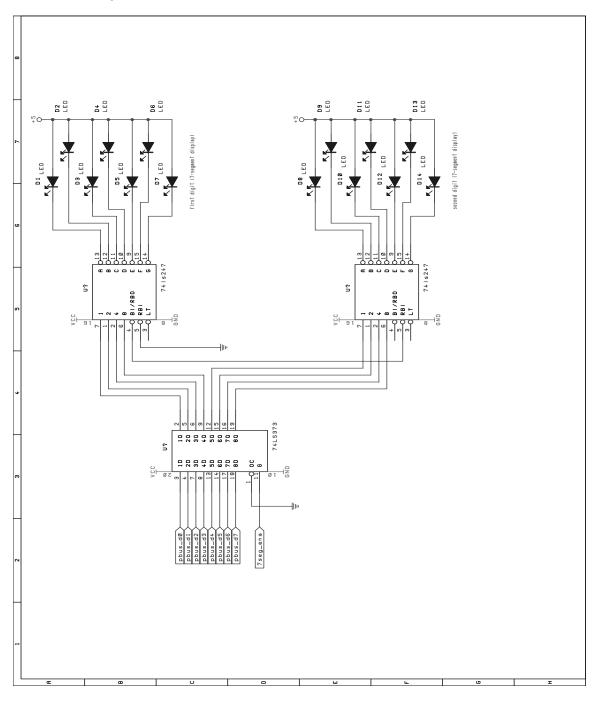

| 47       | Output assign module, 7-segment display decoder and driver schematic 63                                                                                     |

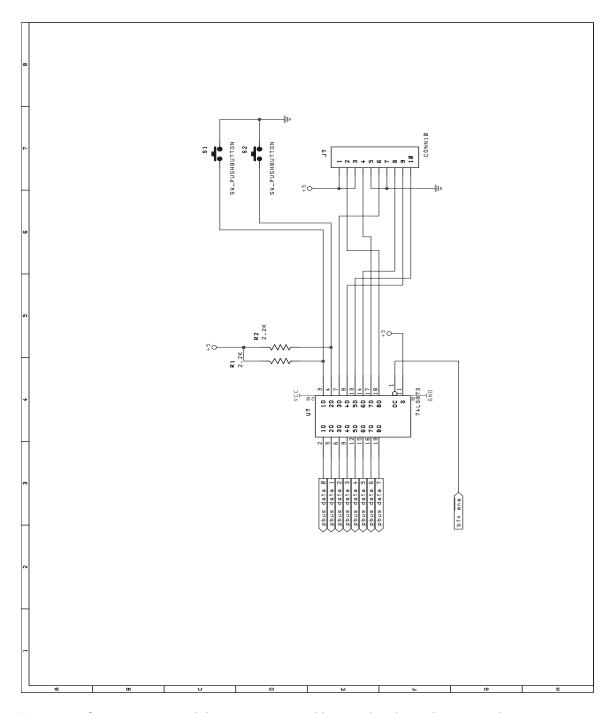

| 48       | Transport control module, address decoding GAL schematic 64                                                                                                 |

| 49       | Transport control module, momentary pushbutton decoder schematic 68                                                                                         |

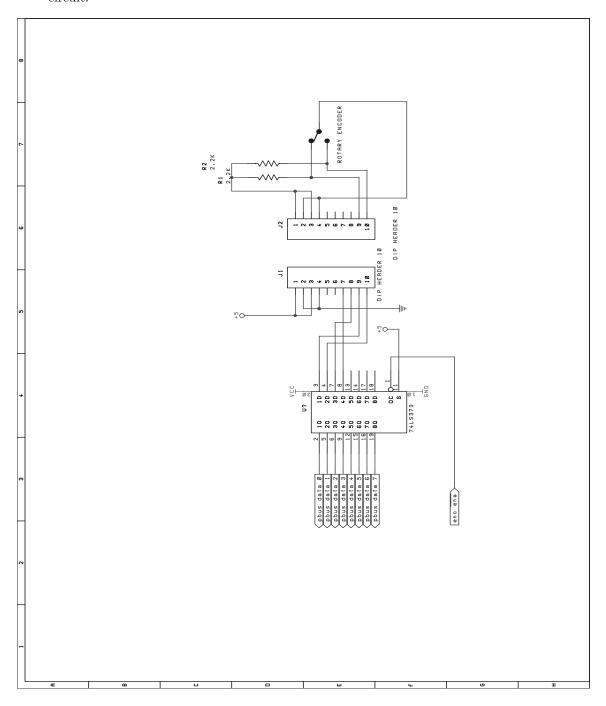

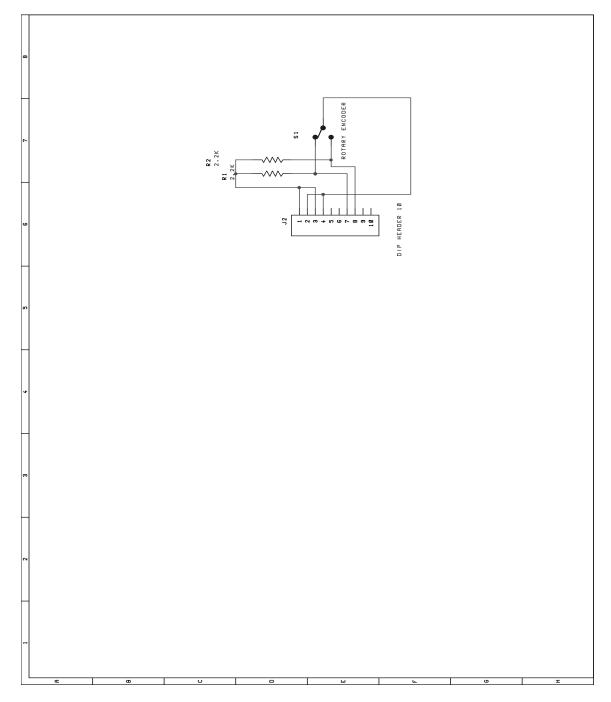

| 50       | Transport control module, rotary encoder interface schematic. This also acts as the interface for the encoder on the universal interface module             |

| 51       | Transport control module, LED driver schematic 6                                                                                                            |

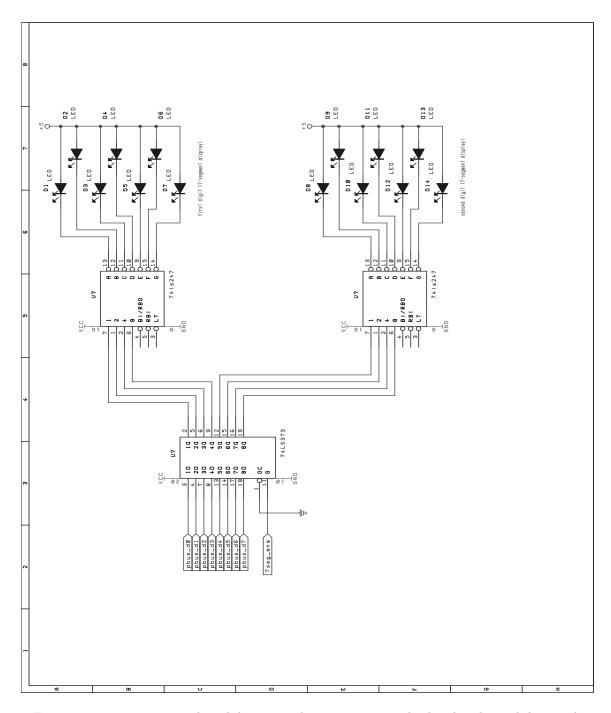

| 52       | Transport control module, track select 7-segment display decoder and driver schematic. 68                                                                   |

| 53       | Transport control module, time indicator 7-segment display decoder and driver schematic                                                                     |

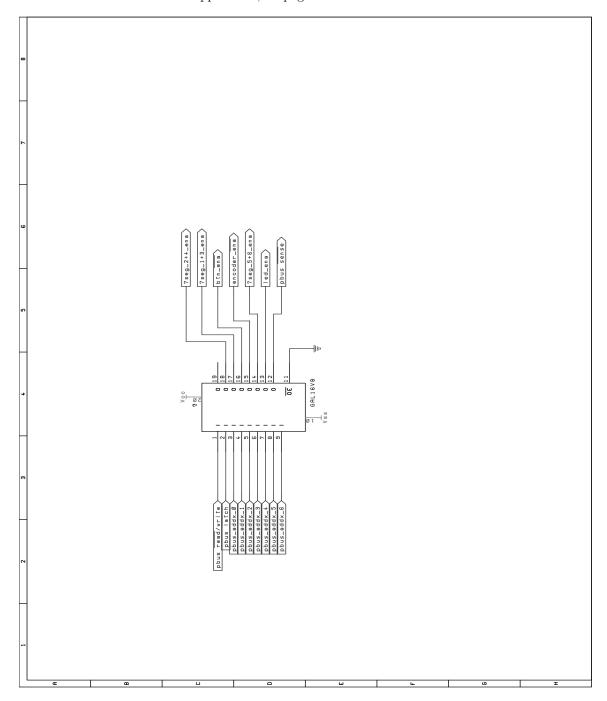

| 54       | Universal user interface submodule, rotary encoder schematic. This circuit con-                                                                             |

| <u> </u> | nects to the transport control encoder interface                                                                                                            |

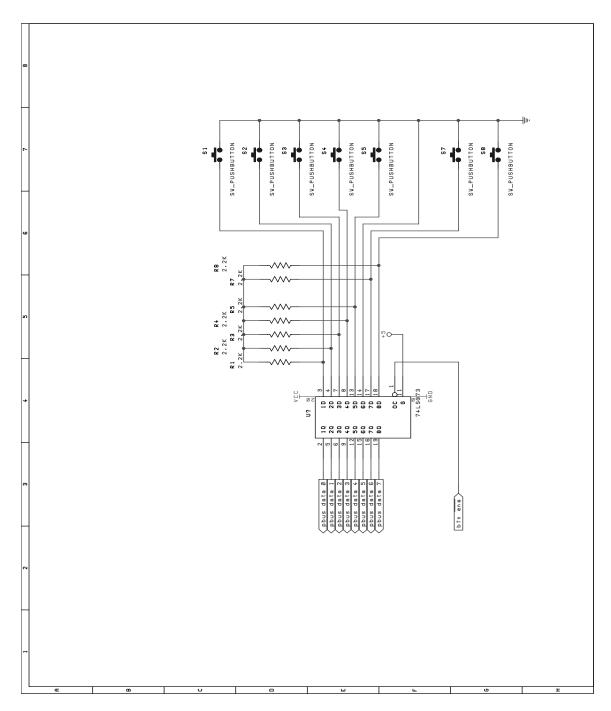

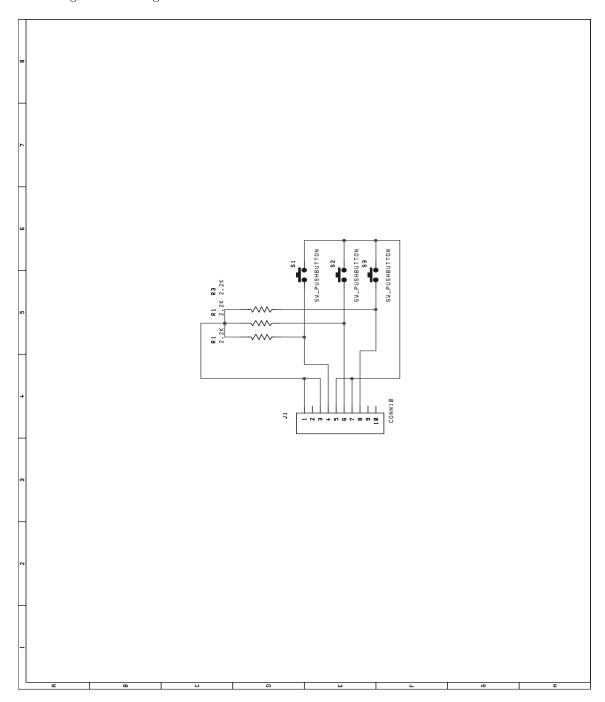

| 55       | Universal user interface submodule, momentary pushbutton interface schematic.                                                                               |

|          | This circuit connects to the output assign button interface                                                                                                 |

| 56       | Cue stack submodule, momentary pushbutton interface schematic. This circuit                                                                                 |

|          | connects to the output assign button interface                                                                                                              |

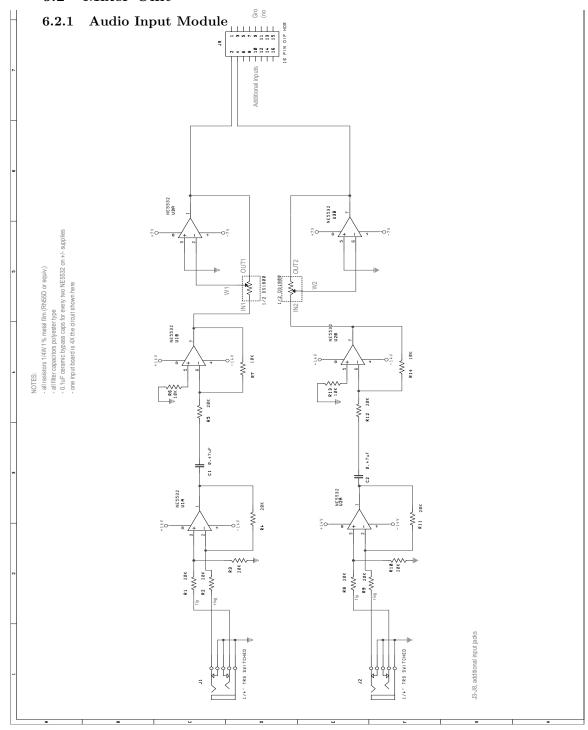

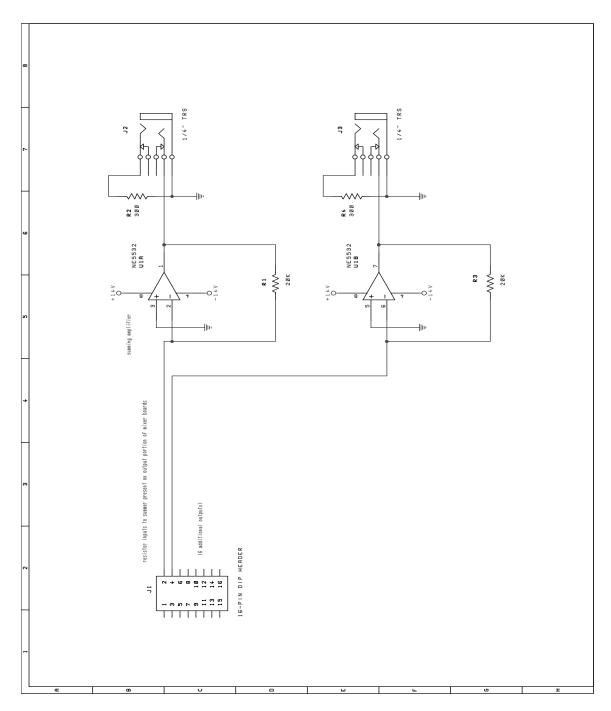

| 57       | Audio input module, line receiver, buffer, and gain adjust schematic (2/8 of mod-                                                                           |

|          | ule)                                                                                                                                                        |

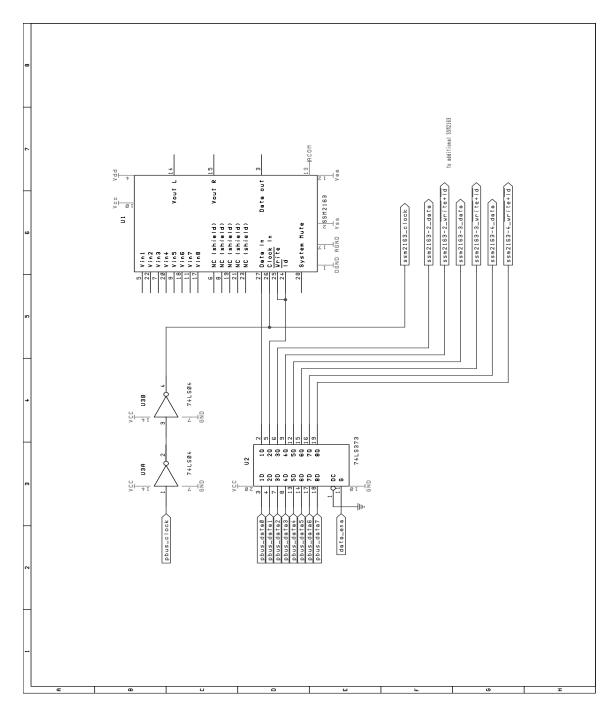

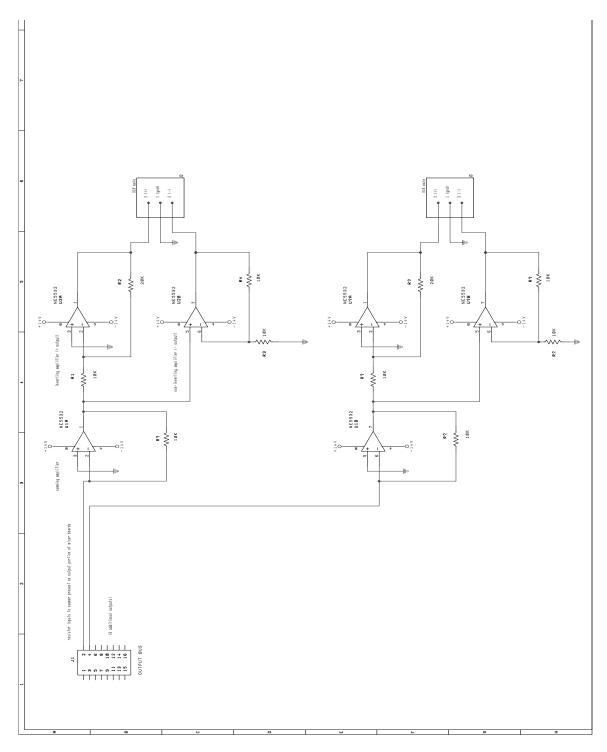

| 58       | Audio mix module, analog circuit schematic (1/4 of module)                                                                                                  |

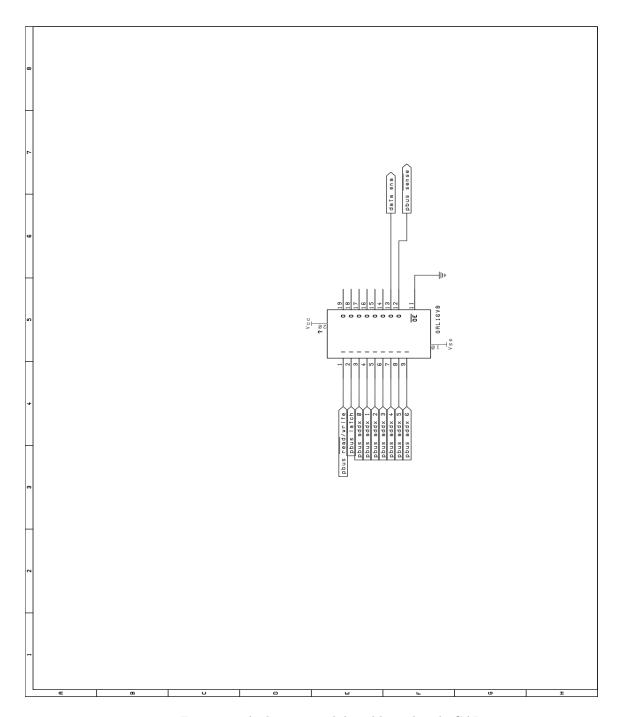

| 59       | Audio mix module, address decode GAL                                                                                                                        |

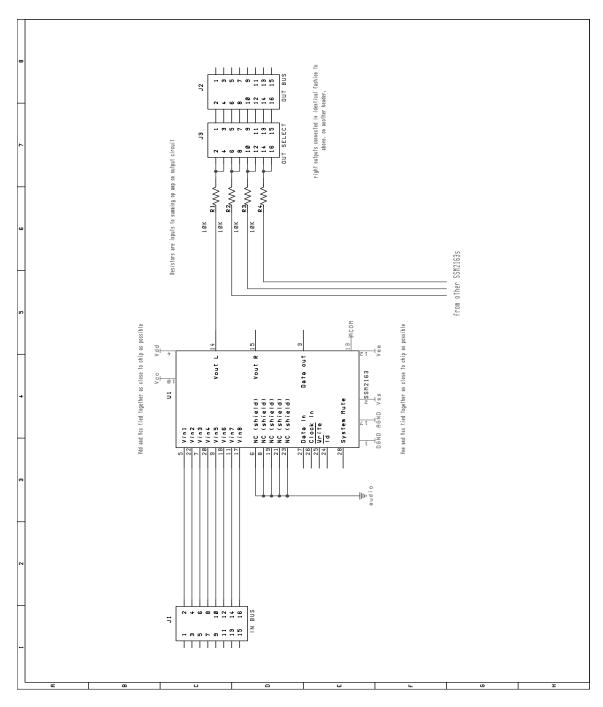

| 60       | Audio mix module, digital circuit schematic (1/4 of module)                                                                                                 |

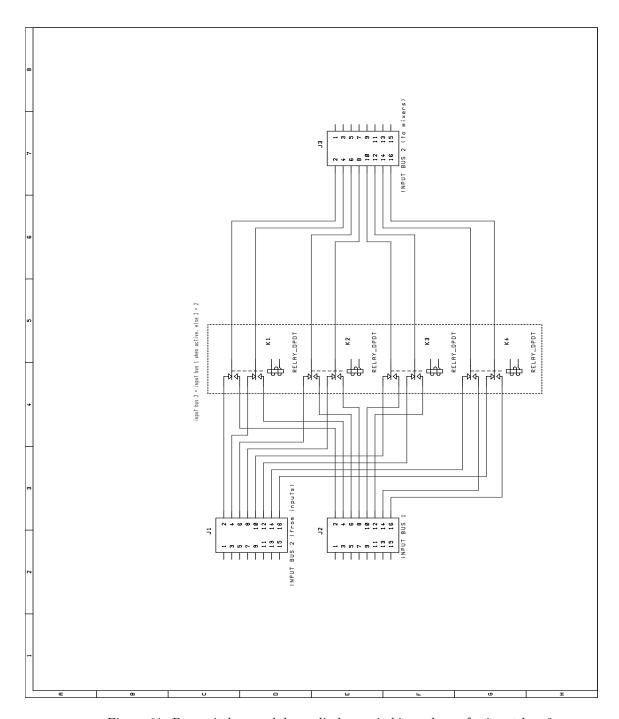

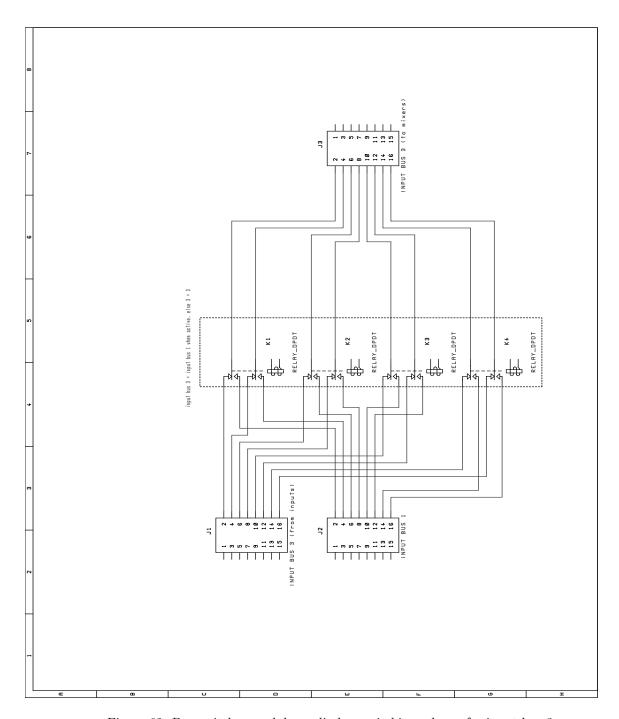

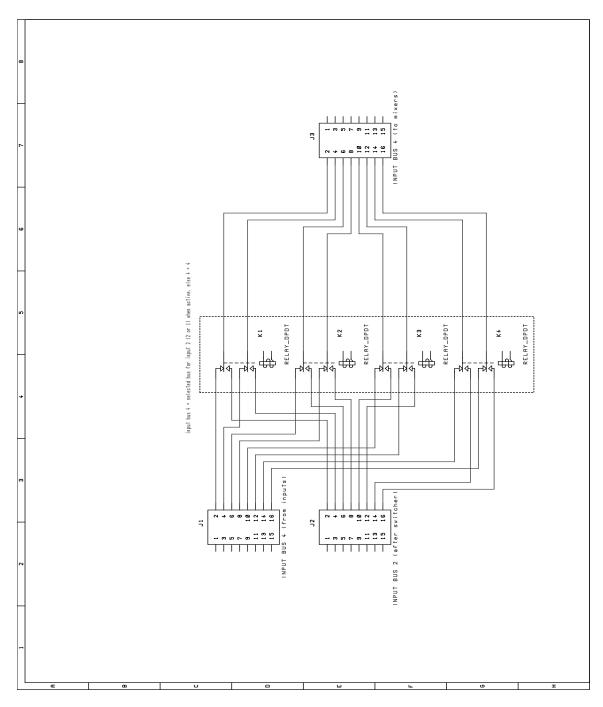

| 61       | Bus switcher module, audio bus switching scheme for input bus 2                                                                                             |

| 62       | Bus switcher module, audio bus switching scheme for input bus 3 80                                                                                          |

| 63       | Bus switcher module, audio bus switching scheme for input bus 4 8.                                                                                          |

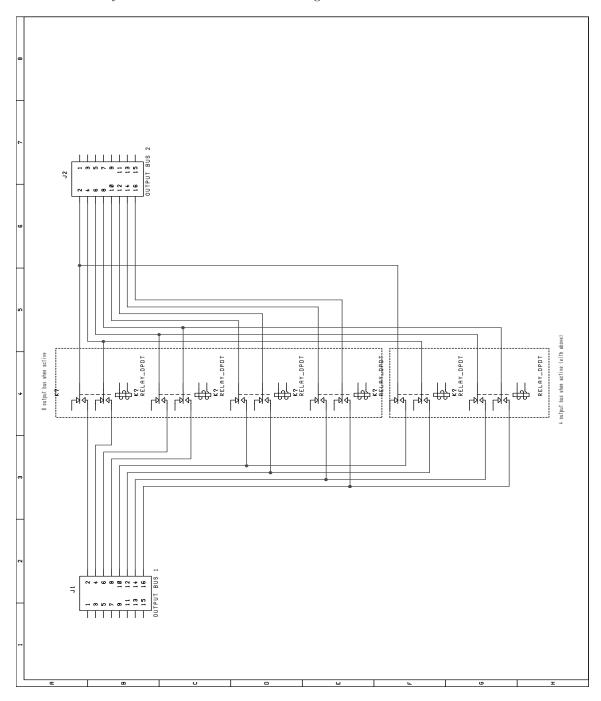

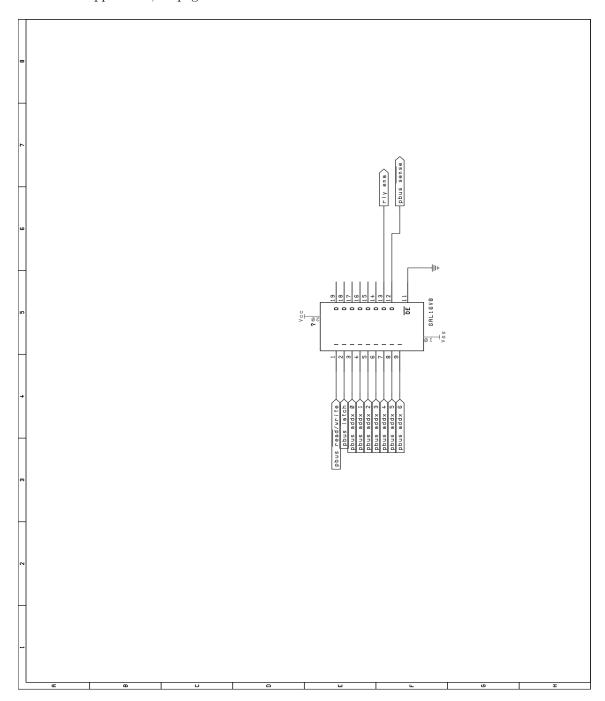

| 64       | Bus combiner module, output bus combination schematic                                                                                                       |

| 65       | Bus switcher/combiner module, address decoding GAL                                                                                                          |

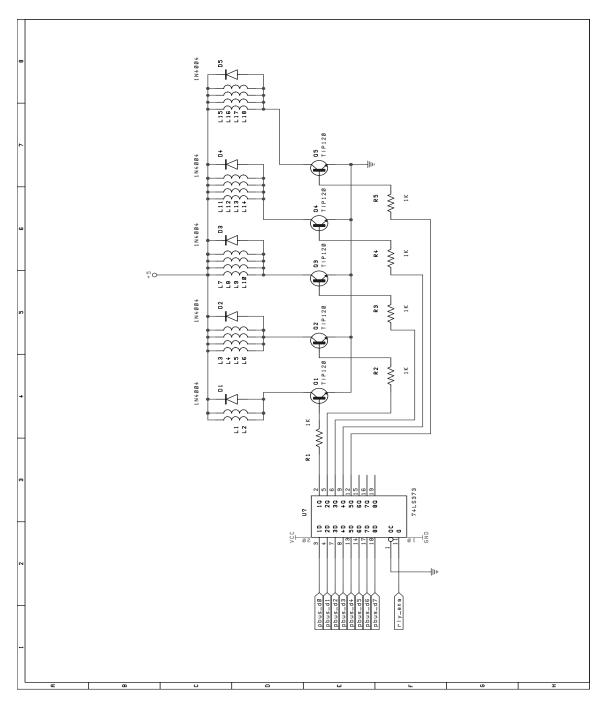

| 66       | Bus switcher/combiner module, digital and relay driver schematic 8                                                                                          |

| 67       | Audio output module, unbalanced driver schematic                                                                                                            |

| 68       | Audio output module, balanced driver schematic                                                                                                              |

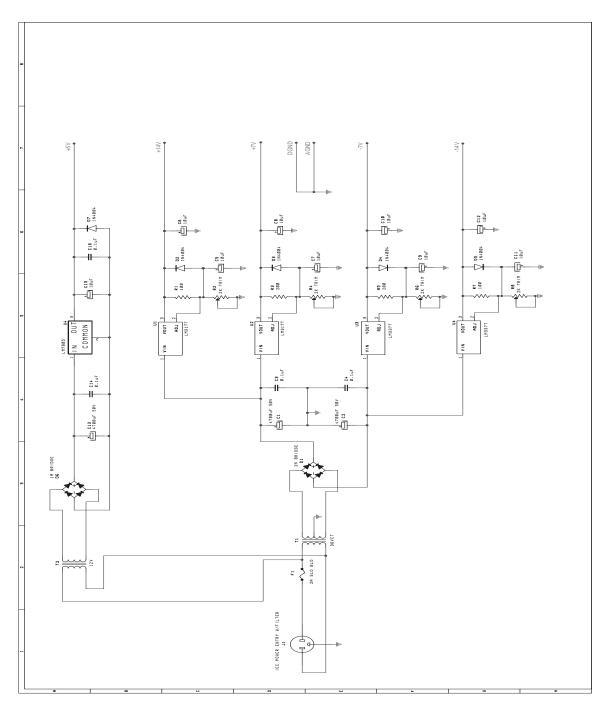

| 69<br>70 | Audio mixer unit, power supplies for analog and digital circuitry 89  Screen shot from the Cypress Warp VHDL functional simulator                           |

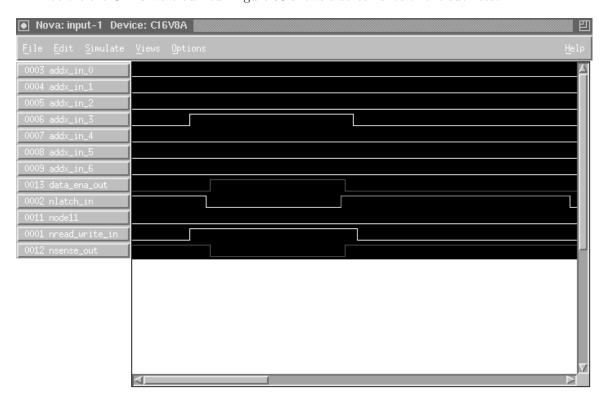

| 70<br>71 | Screen shot from the Cypress Warp VHDL functional simulator                                                                                                 |

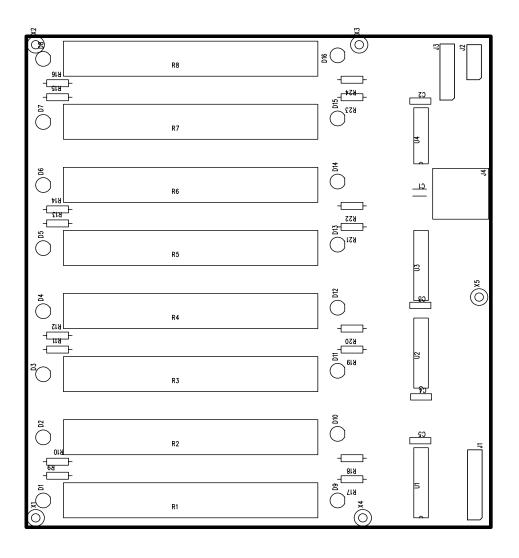

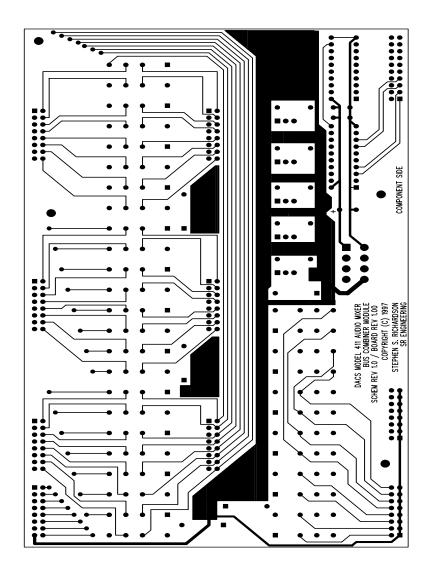

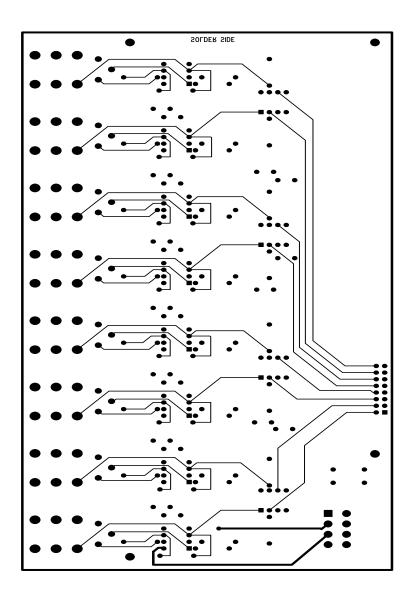

| 72       | Fader module PCB, component-side routing                                                                                                                    |

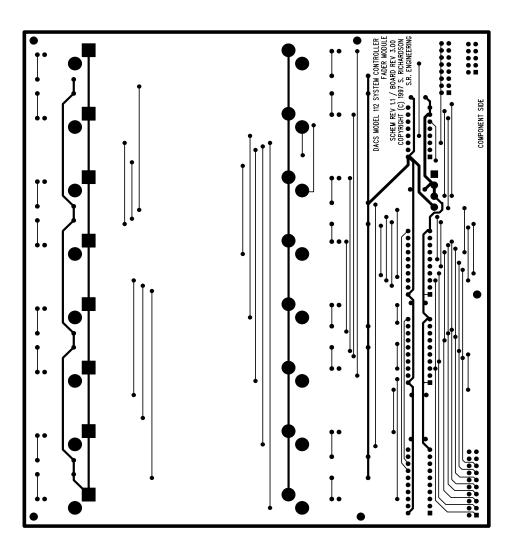

| 73       | Fader module PCB, solder-side routing                                                                                                                       |

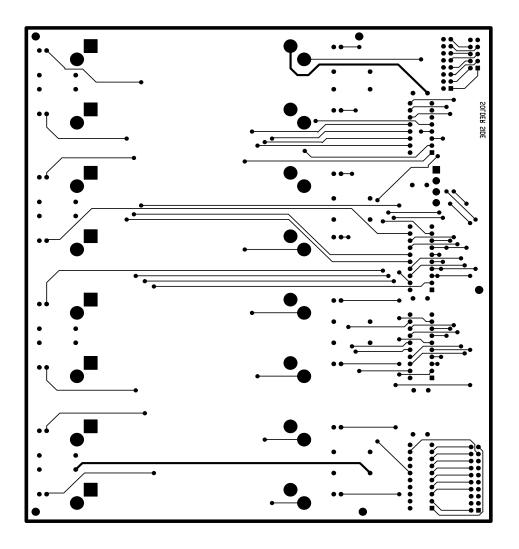

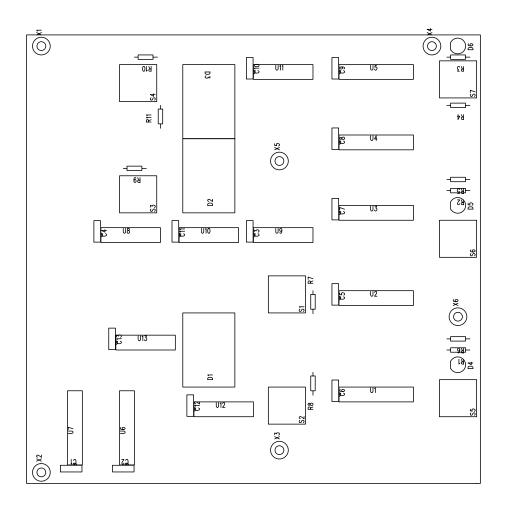

| 74       | Output assign module PCB, silkscreen/assembly drawing                                                                                                       |

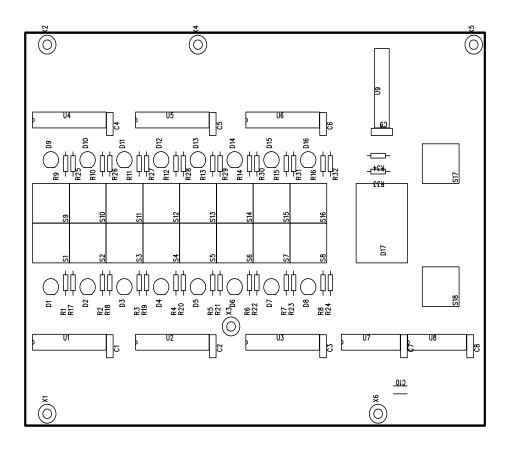

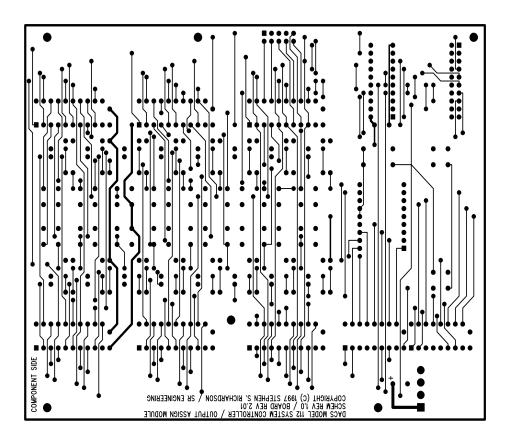

| 75       | Output assign module PCB, component-side routing                                                                                                            |

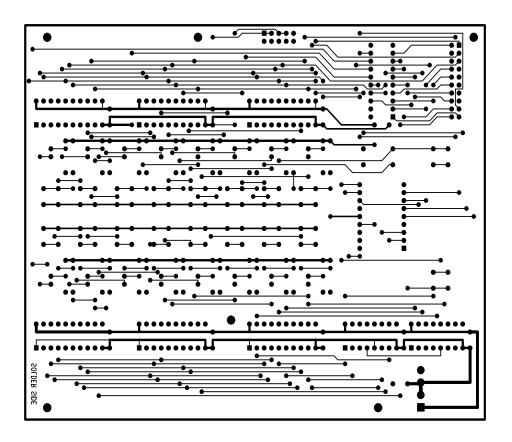

| 76       | Output assign module PCB, solder-side routing                                                                                                               |

| 77       | Transport control module PCB, silkscreen/assembly drawing                                                                                                   |

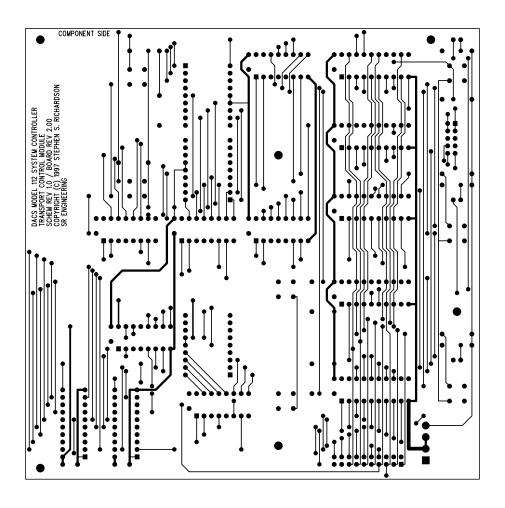

| 78       | Transport control module PCB, component-side routing                                                                                                        |

| 79       | Transport control module PCB, solder-side routing                                                                                                           |

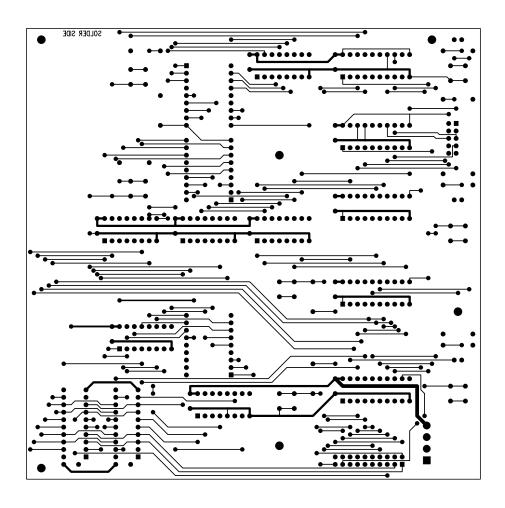

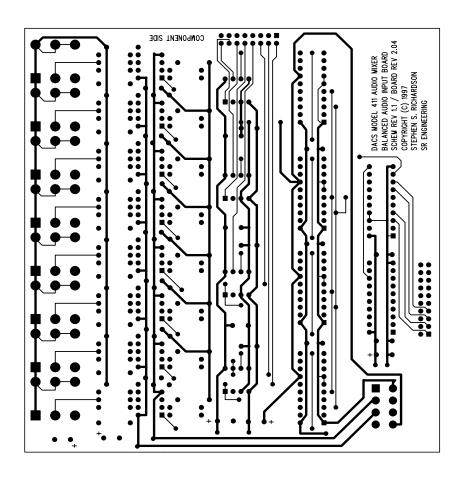

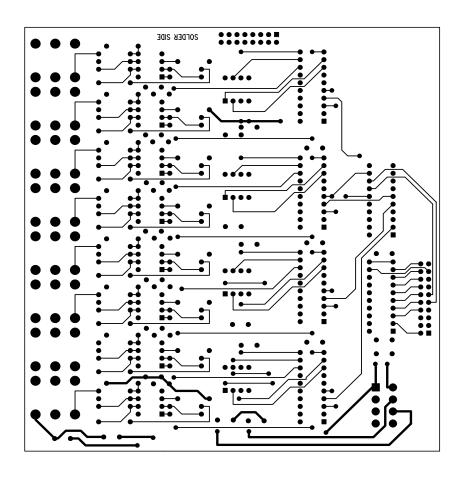

| 80       | Audio input module PCB, silkscreen/assembly drawing                                                                                                         |

| 81       | Audio input module PCB, component-side routing                                                                                                              |

| 82       | Audio input module PCB, solder-side routing                                                                                                                 |

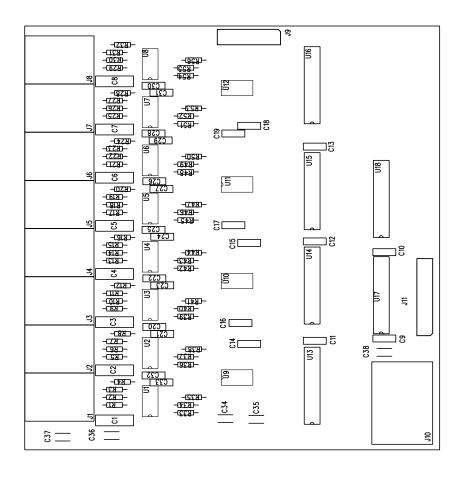

| 83       | Audio mix module PCB, silkscreen/assembly drawing                                                                                                           |

| 84       | Audio mix module PCB, component-side routing                                                                                                                |

| 85       | Audio mix module PCB, solder-side routing                                                                                                                   |

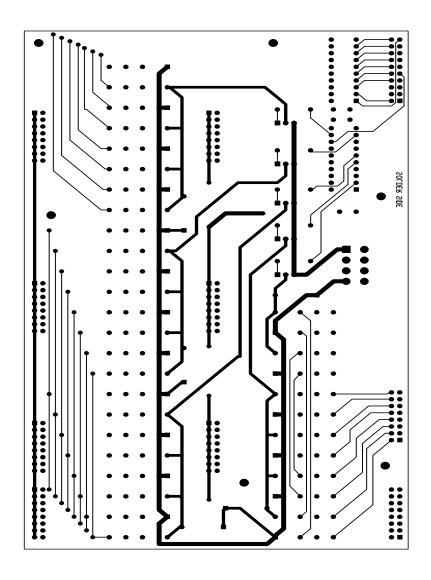

| 86  | Audio bus switcher/combiner PCB, silkscreen/assembly drawing                    | 11 |

|-----|---------------------------------------------------------------------------------|----|

| 87  | Audio bus switcher/combiner PCB, component-side routing                         | 12 |

| 88  | Audio bus switcher/combiner PCB, solder-side routing                            | 13 |

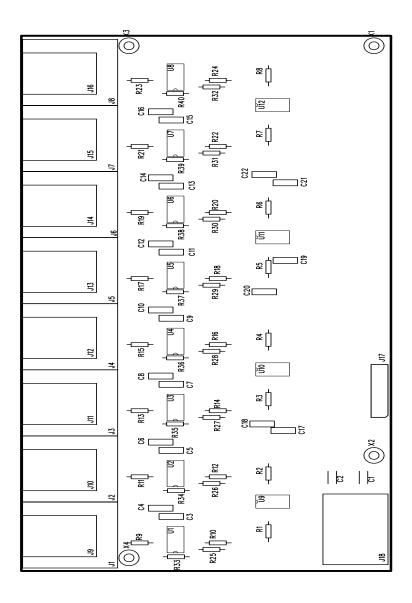

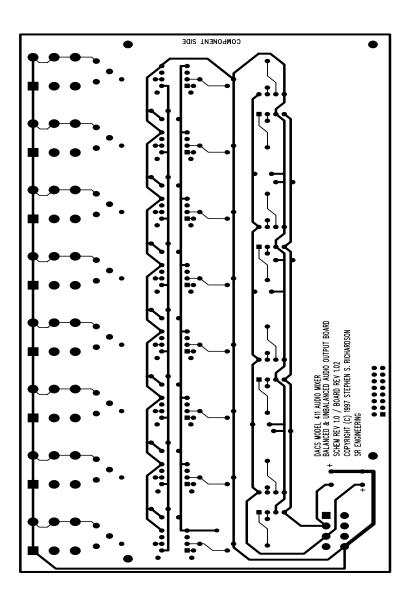

| 89  | Audio output module PCB, silkscreen/assembly drawing                            | 14 |

| 90  | Audio output module PCB, component-side routing                                 | 15 |

| 91  | Audio output module PCB, solder-side routing                                    | 16 |

| 92  | Control board chassis layout, top view                                          | 17 |

| 93  | Mixer unit chassis layout, top view                                             | 18 |

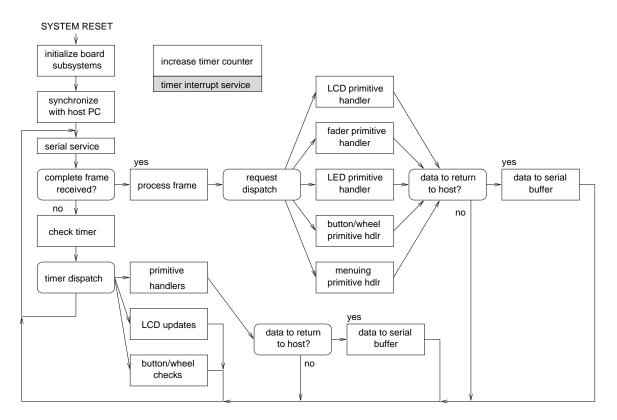

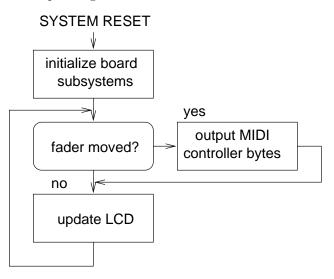

| 94  | Control board firmware, modular overview                                        | 19 |

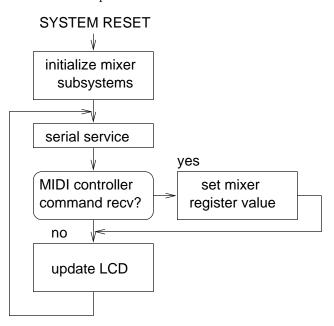

| 95  | Control board firmware, intelligent mode functional flow diagram                | 20 |

| 96  | Control board firmware, dumb mode functional flow diagram                       | 21 |

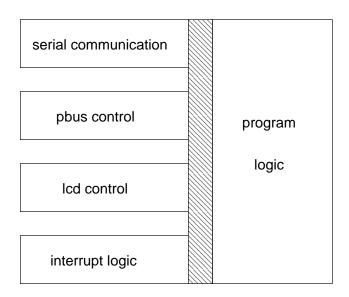

| 97  | Mixer unit firmware, modular overview                                           | 22 |

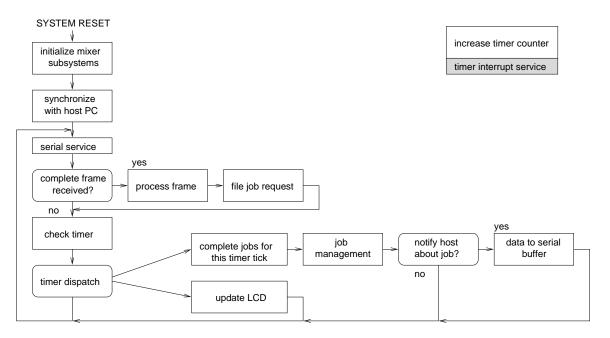

| 98  | Mixer unit firmware, intelligent mode functional flow diagram                   | 23 |

| 99  | Mixer unit firmware, dumb mode functional flow diagram                          | 24 |

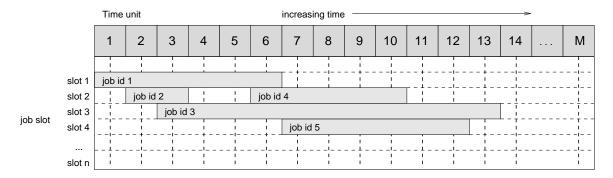

| 100 | Mixer jobs, job slot vs. time                                                   | 25 |

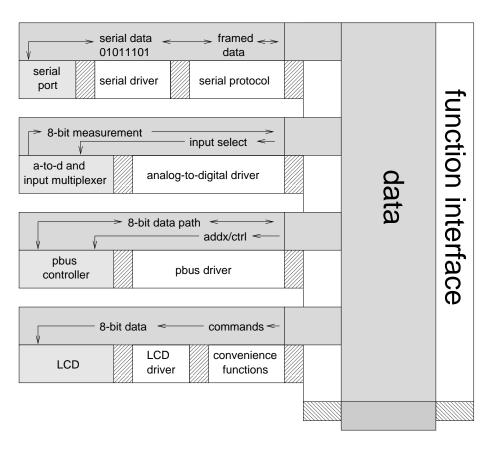

| 101 | DACS firmware library, data flow and function interface overview                | 26 |

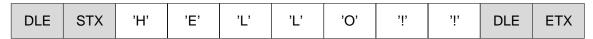

| 102 | Serial protocol, 'clean' data framed for transmission                           | 27 |

| 103 | Serial protocol, 'unclean' data character stuffed and framed for transmission 1 | 28 |

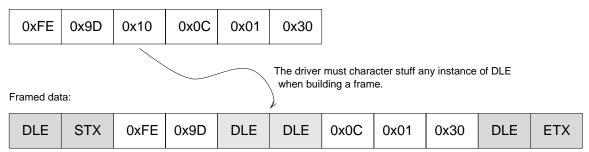

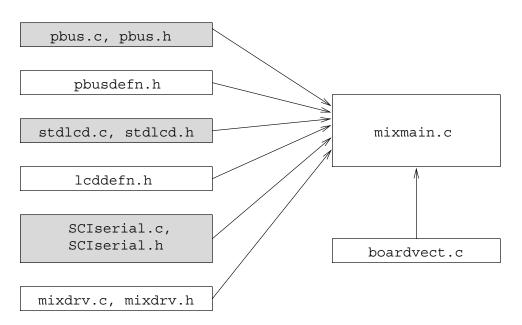

| 104 | DACS firmware library, module view with functions                               | 29 |

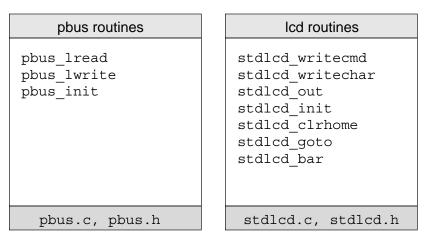

| 105 | ,                                                                               | 30 |

| 106 | Mixer unit firmware, module view                                                | 31 |

| 107 | System view of DACS software components                                         | 75 |

| 108 | VI                                                                              | 76 |

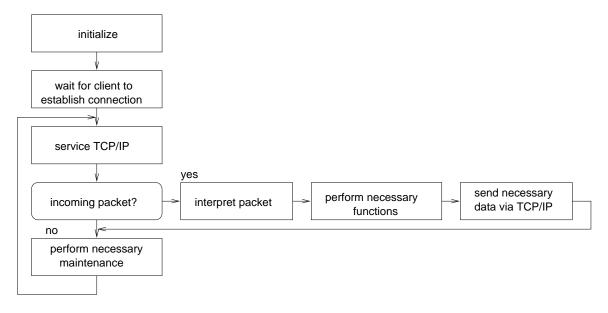

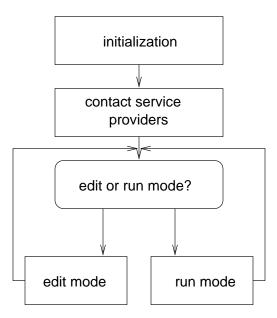

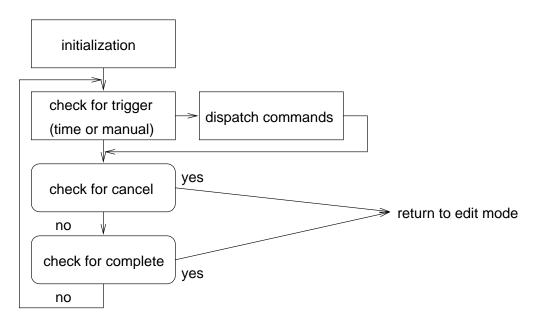

| 109 | Functional flow diagram of q2q at the top level                                 | 77 |

| 110 | Functional flow diagram of q2q in the run mode                                  | 78 |

| 111 | Functional flow diagram of q2q in the edit mode                                 | 78 |

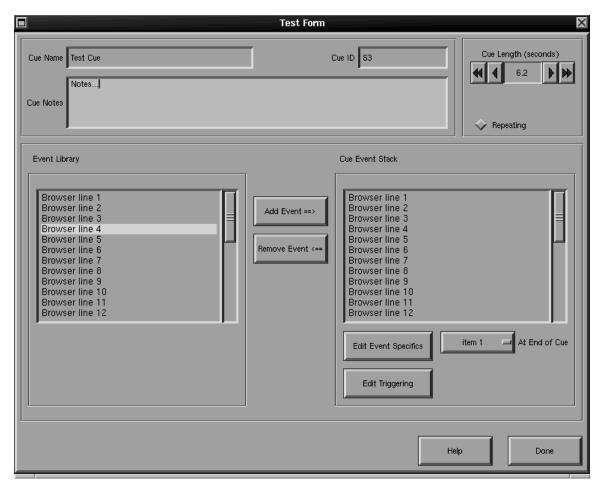

| 112 | Preliminary form for "edit cue" function                                        | 79 |

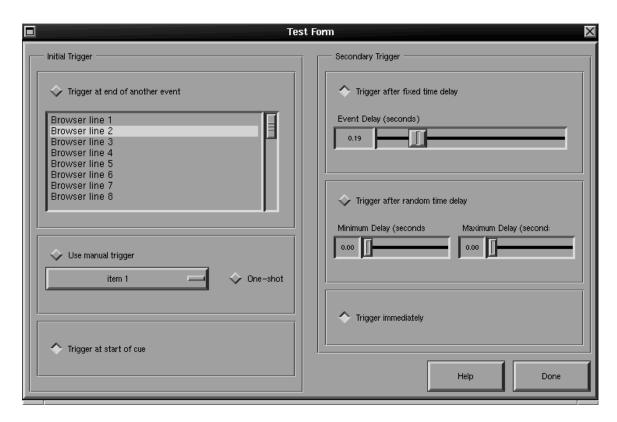

| 113 | Preliminary form for "edit event trigger" function                              | 80 |

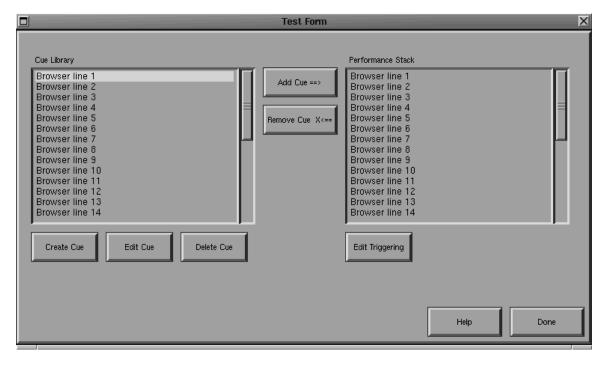

| 114 | Preliminary form for "build performance stack" function                         | 80 |

# List of Tables

| 1  | Maximum calculated power supply currents. † 13mA maximum supply current for     |     |

|----|---------------------------------------------------------------------------------|-----|

|    | NE5532 dual op-amp. Assumes full system with all balanced input and output      |     |

|    | boards. ‡15mA maximum supply current for SSM2163 mixer IC. Assumes full         |     |

|    | system with sixteen audio mixer modules.                                        | 88  |

| 2  | Fader module, bill of materials                                                 | 94  |

| 3  | Output assign module, bill of materials                                         | 94  |

| 4  | Transport control module, bill of materials                                     | 94  |

| 5  | Audio input module, bill of materials                                           | 103 |

| 6  | Audio Mix Module, bill of materials                                             | 103 |

| 7  | Bus combiner/switcher, bill of materials                                        | 110 |

| 8  | Audio output module, bill of materials. † For balanced configuration only. ‡For |     |

|    | unbalanced configuration only.                                                  | 110 |

| 9  | Control board user interface primitives                                         | 122 |

| 10 | Mixer job table                                                                 | 125 |

| 11 | Axiom CMD-11A8 MC68HC11-based single board computer, memory map $(1/2)$ .       | 235 |

| 12 | Axiom CMD-11A8 MC68HC11-based single board computer, memory map (2/2).          | 236 |

| 13 | Axiom CMM-11A8 MC68HC11-based single board computer, memory map $(1/2)$ .       | 237 |

| 14 | Axiom CMM-11A8 MC68HC11-based single board computer, memory map (2/2).          | 238 |

## 1 Executive Summary

## 1.1 What Does the System do?

The Distributed Audio Control System (DACS) provides a means for automating common tasks performed in various audio engineering contexts. Automated mixing, compact disc audio cueing, digital audio control, and MIDI device control can be automated using the DACS. This allows complex sequences of events to be controlled with an ease not previously available.

DACS provides these automation capabilities in two distinct ways. Integration with existing off-the-shelf MIDI software provides a means for adding automation to a home-studio environment with relative ease. Additionally, a custom software environment allows development of audio scripts which can be cued manually or synced to a time source. This capability means the DACS is also equally at home in a broadcast audio or theatre audio setting.

## 1.2 Why Design and Implement this System?

First and foremost, there are no systems on the market currently that offer as many features as DACS for the projected cost. This means that powerful capabilities can be brought within reach of those working with a modest budget.

Secondly, the features of DACS are of use to me, personally. Much of my life revolves around audio work in studio, theatre, and live settings. This project is an outlet for ideas I have had for ways of improving capabilities in these areas.

### 1.3 Project Goals

When the project began, a general set of goals was established. First, it was desirable to design a practical, marketable product. To do this would require careful balance of quality, affordability, and expandability. Secondly, and most importantly, it was decided that the system would be implemented, producing a product as near to production quality as possible.

These goals were very nearly met. The hardware is functional, with only some performance issues left to conquer. Firmware and software still require additional development time to implement the complete system design, but early tests show that the system has a lot of potential.

#### 1.4 Deliverables

This MQP has produced the following materials:

- DACS Model 411, an automated, self-contained line-level mixer in a 3-space rack-mount form factor. The prototype unit supports 32 balanced or unbalanced inputs, eight balanced outputs, and eight unbalanced outputs. The prototype can mix 32x4, 16x8, 8x16, or 4x8x4 channels, and is expandible to 32x16 capability.

- DACS Model 112, a self-contained system control board. Traditional audio controls such as faders and buttons are presented, with the addition of liquid crystal and LED displays. The board provides a powerful, intuitive way to use and program the components of the DACS.

- Linux backend software, cdaudio\_daemon, a software component to provide integration of the audio functionality of computer-hosted compact disc drives with DACS. TCP/IP is employed as a means of communication with other DACS elements, furthering the distributed concept.

- Linux backend software, midictrl, a software component that brings DACS support to off-the-shelf MIDI packages such as *Cakewalk Pro Audio*. The software performs appropriate translations to allow bidirectional interoperation between MIDI devices and the subsystems of DACS.

• **Design Specification**, this document. This document details the design and development of both the completed and uncompleted portions of the project. The design sections for firmware and software are obvious starting points for expansion and improvement of the project.

#### 1.5 Conclusions

For me, DACS is a project of longer-term than an MQP can provide. The MQP has provided a solid foundation upon which the remaining unimplemented firmware and software designs may stand. Even though the project did not meet the initial goals to the letter, it still seems that they were well met. Given the scope of the work completed on the project, and the degree to which it is complete, this makes sense.

DACS is a project that, at least in concept, began for me over two years ago. Considering the potential I see for this system, it is quite likely that development will continue beyond the scope of the MQP. The technology of DACS is viable, affordable, and directly applicable to many applications. Over time, it is hoped that it can be evolved into a marketable product.

The following is a list of known problems or incomplete tasks: (note: not all of these may make sense until this design document has been read through.)

- There is a noise floor approximately 50dB down in the mixer unit. This has not been investigated thoroughly, but it is suspected that it may be due to a grounding issue with the SSM2163 mixer chips.

- Digital "hash" noise can be heard in the outputs of the mixer unit during periods of heavy microcontroller activity. This is likely due to the complete lack of shielding in the unit.

- The bus combining/switching logic in the mixer unit is noisy during switching periods. This is heard as a loud "pop" on the outputs of the unit. It is suspected that this is due to the large switching currents used in the relays, and/or residual DC offsets between buses.

- The mis-designed input trim section requires a re-design and engineering fix. This is a relatively important piece of functionality that is missing in the prototype mixer unit.

- The microcontrollers chosen for the task may not be sufficiently powerful. Early tests are inconclusive, but it is a distinct possibility that a more powerful microcontroller needs to be used.

- The firmware and software are still at a relatively immature stage, from an implementation point of view. For the system to truly be useful, these areas need to be addressed.

- The control board requires another LCD, three buttons, and a data wheel to be mounted. Painting and silkscreened artwork also need to be completed.

This may seem like a large list, but given the sheer number of things that went *correctly*, it is a relatively small list. These items are among the first that will be addressed as the project progresses beyond being an MQP.

## 2 Introduction

This project represents a complete re-thinking and re-engineering of an independent study project completed between March and May of 1995 by myself and fellow WPI student and long-time friend Michael Andrews. The original project saw the development and implementation of a simple computer-controlled mixer, combined with software for controlling CD-ROM drives and PC sound cards. A simple text-based front end was written to facilitate execution of user-cued events at the push of a button. This system was developed and used in three large theatre productions, serving as the audio control system for all of the sound effects.

While the original system functioned reasonably well for the time frame in which it was developed (approximately 6 weeks!), it had several shortcomings that needed to be addressed. It was clear in my mind that the product was viable and useful technology for theatre audio applications. Research at the time showed no products with similar capabilities in our price range, and real-world tests showed that the system removed much of the human error inherent in manually-run audio.

A year and a half passed with no major improvements to the original system. When it came time to chose an MQP, it seemed natural to take some concepts from the original system and develop an entirely new system under a more reasonable development schedule. It was clear from the outset of the project that, while the development time frame was more reasonable than the original, the project was still extremely ambitious, especially for a one-person hardware, firmware, and software design and development team.

The first term was spent largely doing overall system design and schematic work. PC board design, chassis fabrication, and PC board stuffing were completed during the second term. Term three largely involved systems testing and integration, firmware and software design and coding, and preparation for project presentations. The final term, an optional one, was used to re-design much of the software, begin some software implementation, and to wrap up loose ends of the project, such as completing the documentation. By no means do I consider the project to be completed. I intend to develop it further, to expand the capabilities and quality of the overall system.

## 2.1 Design Methodologies

The remainder of this document presents the design and implementation of the hardware, firmware, and software that comprise the DACS. For most design work, a top-down methodology was chosen, except in cases where it made sense to work from the low-level and the high-level simultaneously. Individual hardware and software component specifications were derived from an overall system design, which was formed using a tabula rasa approach. Essentially, this involved starting with a clean slate rather than preconceived notions from any previous project work. Only after some preliminary design work was done with this method were learnings from previous work introduced. The resulting synthesis was then checked for practicality. The whole process was iterated until a reasonable design was achieved. This process was carried out at various levels of complexity, right down to the component level in hardware, and code level for firmware and software.

At several points down the development chain, it made sense to re-evaluate goals and specifications set at a higher level. In some instances, it was realized that some high-level goals could not be achieved due to problems at lower levels. In most cases, though, an attempt was made to temper high-level goals and specifications with enough real-world knowledge to avoid any major problems or re-working of the original designs.

At the highest level, the two custom pieces of hardware ended up, in the end, to be very similar to what was originally envisioned. Early renderings, shown in later sections, very closely match the final products. This seems to be a good indication that the high-level design goals were set ambitiously (due to the amount of work it took to get the products to that point), but not unrealistically (due to the fact that it actually is at that point).

## 2.2 Application Analysis

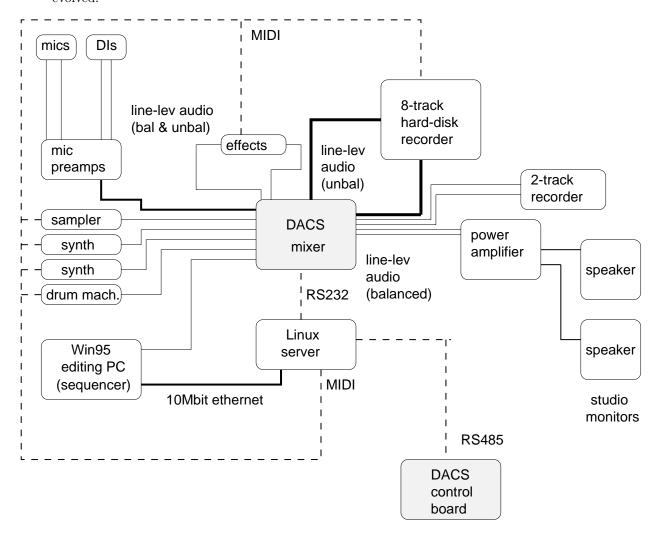

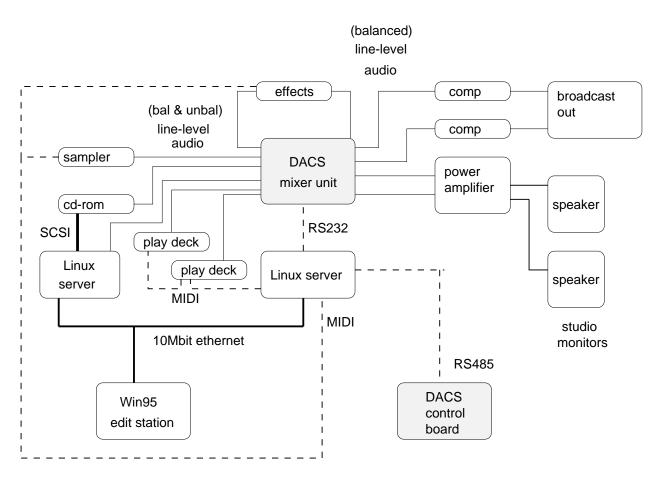

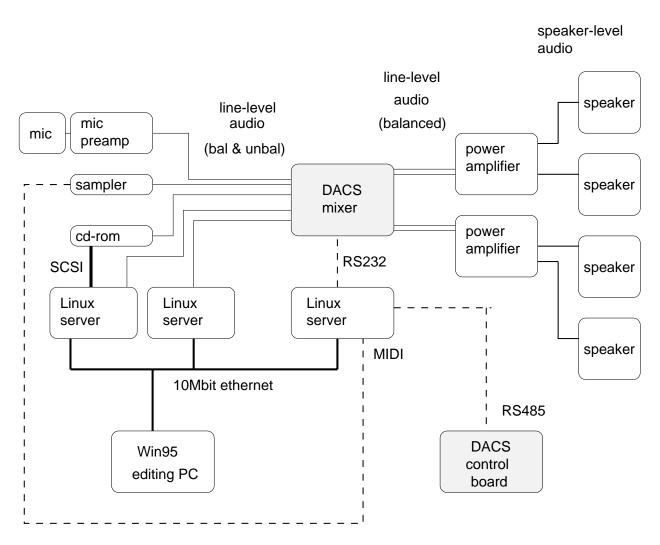

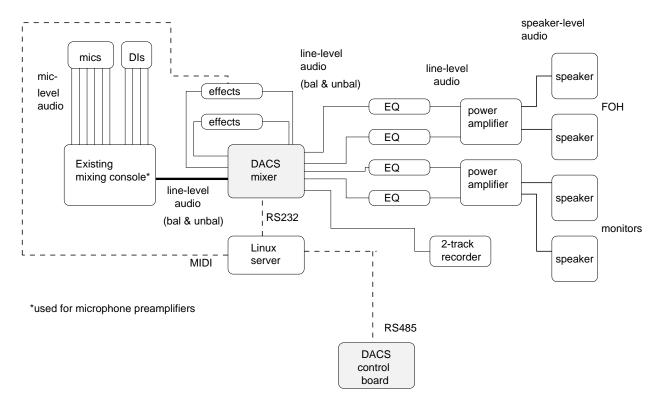

In order to properly form a set of specifications for the components of DACS, a set of potential applications of the system was derived. Four contexts were chosen: a home studio setup, a broadcast application, a theatre application, and a live sound application. Figures 1, 2, 3, and 4 show schematic representations of these possible configurations. In each figure, shaded boxes indicate custom hardware, developed in this MQP. Unshaded boxes indicate off-the-shelf hardware. Custom software runs on each of the computers present in the diagrams. The diagrams have since gone through many iterations since the initial diagrams, hence now reflect actual details of the DACS implementation. Initially, several different diagrams were drawn, out of which these evolved.

Figure 1: Typical DACS-based home studio configuration.

Through studying potential applications and applying what was learned with the previous system, a rough set of specifications was derived. A partial list is shown below:

- Custom audio hardware should support balanced and unbalanced line-level signals.

- Custom audio hardware should be of semi-professional studio quality, dictating relatively low noise floor and THD specifications. This is an important improvement over the original system, which had noise problems.

Figure 2: Typical DACS-based broadcast application.

Figure 3: Typical DACS-based theatre audio application.

Figure 4: Typical DACS-based live sound application.

- Integration with existing MIDI systems would be beneficial, both in terms of functionality and in terms of reduced time expenditure. This integration would not only include MIDI hardware, but existing MIDI sequencing software.

- If possible, existing audio control standards should be used, to provide compatibility between devices.

- Some applications are set in an environment where syncing to SMPTE time codes would be beneficial for automation purposes.

- Overall, the system needs to be flexible, and dynamically expandible and configurable.

- An intuitive, lucid way of programming and controlling the system must be created. A major shortcoming of the original system was the lack of a decent user interface.

- The use of inexpensive off-the-shelf hardware, such as CD-ROMs for compact disc cueing, provided a significant cost advantage in the first system. This concept should be applied to the DACS.

The two pieces of custom hardware, the DACS mixer and the DACS control board, were settled upon as reasonable devices to design and prototype for the MQP. Other pieces of application-specific hardware were considered, but these two pieces of hardware were applicable to all of the applications considered in the analysis. The DACS mixer is the core of the system, thus it was quite clear that its implementation was necessary. The board was implemented because it is believed that it brings a significant improvement to the usability of the system. The remaining DACS components, firmware and software, were developed to the extent that time permitted.

## 2.3 System Overview

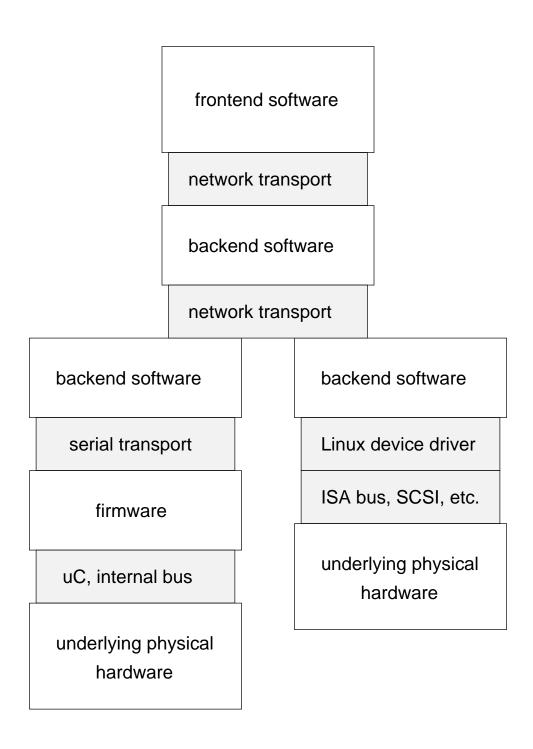

Figure 5 depicts the logical hierarchy of the DACS. Integration of custom and off-the-shelf hardware is accomplished through the means of custom software components. Network transport layers promote the concept of distributed task servicing. DACS service providers appear as services on hosts located on a network, or on a single host (using the internal loopback as a virtual network device). Front-end software accesses individual devices through a series of abstraction layers, such that the actual location and physical characteristics of the underlying hardware providing the service need not be known by that software.

This abstraction paradigm allows generic descriptions of actions to be created which do not depend on the underlying hardware. This would allow, for example, the cues for a touring theatre show to be defined generically, and run on almost any DACS configuration. One can even imagine a CD-ROM with a generic DACS audio script (with all supporting sound effects, etc.) being sold with the script for the play itself.

DACS custom hardware

Off-the-shelf hardware

Figure 5: DACS component hierarchy, generalized view.

## 3 High-Level Hardware Specifications

The high-level hardware specifications are intended to provide an overview of the hardware components developed for the DACS. Decomposition of these specifications is provided in later sections, to the schematic, PC board and component levels.

Some of these specifications have changed over time in a constant attempt to satisfactorily balance the goals set at the system level and the constraints of time, money, and practicality.

#### 3.1 Control Board

The control board is a microcontroller-based remote control unit for the various functions of the DACS. The board shall provide familiar user interfaces for audio mixing, transport, and cue control. In addition, a multi-purpose interface element shall be included, to provide an interface for functions that do not fit into the paradigms mentioned above. Additionally, this interface mechanism shall provide an easily adaptable means for future expansion.

#### 3.1.1 System Description

The user shall be able to control the mixing features of the DACS mixer module via familiar slide potentiometers (faders). The values of these potentiometers shall be digitized with an 8-bit A/D converter, and processed appropriately via the internal microcontroller. Because "flying faders" will not be used on this board due to cost, each channel shall have two LED indicators associated with it to aid in adjusting channel values. The "active" indicator shall light if a particular channel is active in the current mixer/matrix mode. The "grab" indicator, used when editing mix settings, shall light green when the fader has been moved from the current setting, and red when the old value has been "grabbed".

The user shall have control over the channel assignment features of the DACS mixer via a set of pushbutton switches and associated LEDs. The active output channels for a given input channel shall be toggled with these switches. The input channel that is being controlled shall be selectable via two pushbutton switches. An LED display shall provide visual indication of the active channel number.

The user shall be able to control the transports of various physical or virtual audio devices. An interface shall be provided to allow the user to select which device to work with, via a pair of pushbutton switches. Visual indication of the current transport shall be provided via a 16 character alphanumeric LCD. The transport controls shall allow the track index and time index to be adjusted. Track index shall be adjusted via a pair of pushbutton switches. Time index shall be adjusted via a detented rotary encoder wheel. "Play," "Cue," and "Stop" functions shall also be available to the user, via pushbutton switches with LED indicators for visual reference.

The user shall be able to execute a series of pre-programmed cues from the board. These cues may include, but are not limited to, mixer events, transport events, MIDI events, etc. In addition, rudimentary cue stack editing shall be allowed from the board. Cue information shall be presented to the user via a 40x2 LCD. Three buttons shall be used to navigate and execute the cue stack.

The unit shall incorperate an appropriate internal power supply. External connection to this supply shall be made via a standard IEC power connector at the rear of the unit. This power entry unit shall be of the type that filters EMI and RFI interference. It shall be appropriately fused and switchable via a rocker switch.

The board's microcontroller shall communicated with the rest of the DACS via an RS485 4-wire serial interface. This interface shall be presented as a 5-pin male XLR connector, and shall be wired per the DMX512 lighting control specification. This connector was chosen due to its robustness. The adherence to the DMX512 specification merely eliminates any potential equipment malfunction due to accidental interconnection, as DMX512 uses the same connectors,

and will often be present in places this mixer will be used. The serial communication shall take place at 9600 band.

The unit shall be referred to as  ${\bf DACS}$  Model 112 - System Control Board.

## 3.1.2 Specification Sheet

## CONNECTORS

| RS485 control                      | : | (1)  | 5-pin male XLR/Cannon, panel-mount                             |

|------------------------------------|---|------|----------------------------------------------------------------|

| expansion                          | : | (1)  | 25-pin female D-sub                                            |

| power                              |   |      | IEC, with EMI/RFI filter & fuse                                |

| CONTROLS                           |   |      |                                                                |

| channel faders                     | : | (16) | 2-3/8 inch (60 mm) travel<br>linear taper slide potentiometers |

| multi-function                     | : | (2)  | tactile pushbutton switches, PC board mount                    |

|                                    |   | (1)  | detented encoder wheel                                         |

| output assign                      | : | (16) | tactile pushbutton switches, with LED, PC board mount          |

|                                    |   | (2)  | tactile pushbutton switches, PC board mount                    |

| transport                          | : | (4)  | tactile pushbutton switches, PC board mount                    |

|                                    |   | (3)  | tactile pushbutton switches, with LED, PC board mount          |

|                                    |   |      | detented encoder wheel                                         |

| cue stack controls                 | : | (3)  | tactile pushbutton switches, PC board mount                    |

| INDICATORS & DISPLAYS              |   |      |                                                                |

|                                    |   | (16) | T1-3/4 red/green bicolor LEDs                                  |

| channel active                     |   |      | T1-3/4 green LEDs                                              |

| output channel assign              | : |      | green LEDs                                                     |

| +                                  |   |      | dual 7-segment green LED display                               |

| transport function RS485 link data |   |      | green LEDs<br>T1-3/4 green LED                                 |

| transport track & time             |   |      | dual 7-segment green LED displays,                             |

| multi-function display             |   |      | backlit LCD,                                                   |

| martir randoron aropitay           | • | (1)  | 40x8 alphanumeric characters,                                  |

|                                    |   |      | plus 240x64 graphics capability                                |

| transport control display          | : | (1)  | backlit LCD,                                                   |

|                                    |   |      | 16x1 alphanumeric characters                                   |

| cue-stack control display          | : | (1)  | backlit LCD,                                                   |

|                                    |   |      | 40x2 alphanumeric characters                                   |

## ENCLOSURE

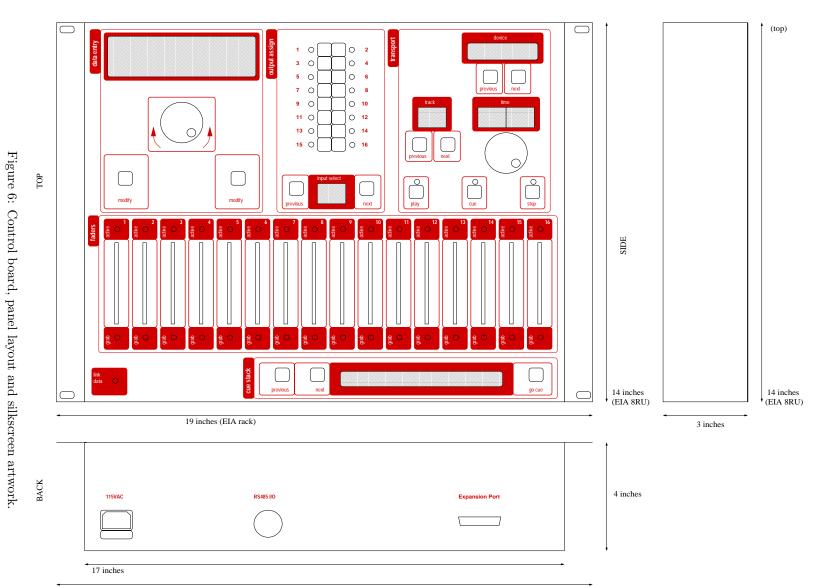

dimensions .....: 19 inches (482mm) wide (EIA rack)

14 inches (356mm) tall (EIA 8 RU)

4 inches (102mm) deep max.

top and rear panel .....: steel (acrylic on prototype) bottom, top and side ....: steel (aluminum on prototype)

color .....: satin black

external component layout : as per layout diagrams, below. panel artwork ..... : single-color silkscreen, white,

laid out as below.

#### CONSTRUCTION

All components shall be PC-board mount style, except where not possible. Liquid crystal displays shall be covered with transparent acrylic or equivalent material. Faders and rotary encoders shall be mounted to the case for additional durability.

#### MARKETING

target retail price ..... : \$899 for base unit

additional modules .....: 16-fader expansion module

16-channel meter bridge

modules connect to expansion port

#### 3.1.3 Panel Layout

The panel layout for the control board is shown in figure 6.

#### 3.1.4 Concept Rendering

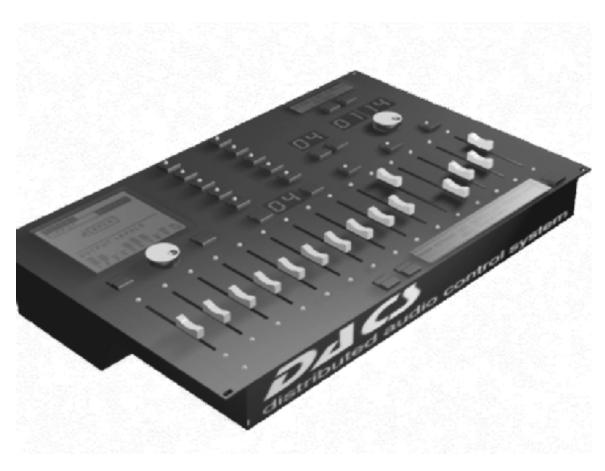

Figure 7 shows the original concept rendering of the control board.

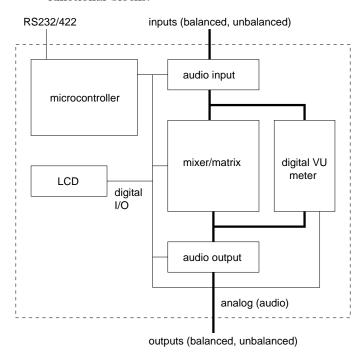

#### 3.2 Mixer Unit

The mixer unit is a microcontroller-based module that shall provide the capability to mix line-level audio signals in an automated fashion. The unit shall be able to mix any of its active inputs to any of its active outputs at any level, within the attenuation range of the mixer. The signal architecture of the mixer/matrix shall be user-reconfigurable, allowing many input channels to be mixed down to few outputs, few inputs to be mixed to many outputs, or an equal number of inputs to be mixed to an equal number of outputs.

#### 3.2.1 System Description

In stock configuration, the unit shall provide thirty-two line-level audio inputs capable of receiving balanced or unbalanced audio signals. Eight balanced and eight unbalanced line-level audio outputs shall also be present on the rear panel of the unit. These outputs may be converted to all balanced or all unbalanced merely by changing modules. Depending on the mode and hardware configuration of the mixer, all inputs and outputs may not be available at a given time.

19 inches (EIA rack)

Figure 7: Control board concept rendering.

The digitally-controlled mixer circuitry shall behave in a logarithmic fashion, to match the response of the human ear. The mixer shall provide from 0dB to 63dB of attenuation capability, in 1dB steps. Additionally, near-infinite attenuation ("mute") shall be provided for each input channel. This dictates that the digital controller for the audio mixer shall have at least 6 bits of resolution.

Digitally controlled switches shall be used to reconfigure the audio paths of the mixer. These switches shall be of the "clickless" type, such that signals may be re-routed without any undesirable noise entering the system.

The unit shall incorperate an 8-bit A/D converter and appropriate analog multiplexer and driver circuitry to allow monitoring of all input and output signals, after the input buffers and before output drivers. This setup shall form the basis for a digital VU meter. The VU meter shall be capable of reporting signals from -10dBu to +18dBu. The converter shall function linearly, with any necessary logarithmic conversion taking place in software. This VU data can be displayed on the mixer unit itself via its LCD and/or transmitted over the microprocessor's serial uplink, to be displayed on a host PC or the DACS control board.

Mixer modes and other relevant information shall be displayed to the user via an LCD panel on the front of the unit. A single LED shall indicate serial link activity. Another LED shall indicate that the unit is powered.

The unit shall be constructed in a modular fashion, such that future upgrades are possible by simply adding or changing cards. The choice of output channel boards shall be left to the user, allowing a mixer with all balanced, all unbalanced, or half balanced and half unbalanced outputs to be constructed. In addition to the upgrade capability, the PC boards shall be designed such that a larger model mixer unit can be built without re-engineering the electronics. Future upgrade options may include, but are not limited to: equalization modules, microphone preamplifier modules, DSP effects engines, and digital audio interfaces (for AES/EBU and S/PDIF-compliant digital audio devices).

The unit shall incorperate linear internal power supplies. Switching power supplies are unacceptable in this unit due to the large quantity of electrical noise they create. Separate power buses for digital and analog circuitry shall be provided, to reduce digital noise in the analog portions of the mixer. These supplies shall be sufficiently capable of powering add-on modules. External connection to these supplies shall be made via a standard IEC power connector at the rear of the unit. This power entry unit shall be of the type that filters EMI and RFI interference. It shall be appropriately fused and switchable via a front-panel rocker switch.

The mixer unit's microcontroller shall communicate with the rest of the DACS via an RS232 3-wire serial interface. This interface shall be presented as a 9-pin female D-subminiature connector, and shall be wired per the RS232 9-pin Data Communications Equipment (DCE) spec. This allows direct connection to a host PC with a straight-through cable. The serial communication shall take place at 19200 baud.

The unit shall be referred to as DACS Model 411 - Modular Automated Audio Mixer.

#### 3.2.2 Specification Sheet

AUDIO INPUT AND OUTPUT

```

Input maximum level .... : +24dBu

Input impedance .... : 10K ohms or greater

Output maximum level ... : +24dBu

Output impedance ... : 100 ohms or less

```

FREQUENCY RESPONSE

20Hz to 30KHz or better, +0dB, 3dB down

any single input to any single output

#### NOISE

80dB S/N ratio or better, +0dBu reference input signal, any single balanced input to any single balanced output

#### TOTAL HARMONIC DISTORTION

0.05% THD or better, any single balanced input to any single balanced output

#### DIGITALLY-CONTROLLED AUDIO MIXER

configurations .....: 8x16, 16x8, 32x4, 4 discrete 8x4 (stock)

16x16, 32x8, 32x16 with expansion options

attenuation .....: 0dB to 63dB resolution .....: 1dB (64 steps)

#### DIGITALLY-CONTROLLED INPUT TRIM

gain .....: at least 12dB resolution .....: 1dB (64 steps)

#### INTERNAL ANALOG-TO-DIGITAL CONVERTER (FOR DIGITAL VU METER)

adc resolution .....: 8 bits

adc acquisition range .....: -10dBu to +18dBu +/- 1dB

adc acquisition points ..... : all audio inputs (post-buffers)

all audio outputs (pre-drivers)

#### CONNECTORS

#### AUDIO INPUT MODULES (4 MODULES TOTAL)

bal/unbal input module ...: (8) tip-ring-sleeve 1/4" phone jacks

#### AUDIO OUTPUT MODULES (2 MODULES TOTAL)

unbalanced output module . : (8) tip-sleeve 1/4" phone jacks

balanced output module ...: (8) panel-mount 3-pin male XLR/Cannon

#### PERMANENT

|                                                           |   | <ul><li>(1) female 9-pin D-sub, wired DCE</li><li>(1) IEC, with EMI/RFI filter &amp; fuse</li></ul> |

|-----------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------|

| CONTROLS                                                  |   |                                                                                                     |

| power                                                     | : | (1) panel-mount rocker switch                                                                       |

| INDICATORS & DISPLAYS                                     |   |                                                                                                     |

| power                                                     | : | (1) T1-3/4 bicolor yel/grn LED                                                                      |

| ENCLOSURE                                                 |   |                                                                                                     |

| dimensions                                                | : | 19 inches wide (EIA rack) 5.25 inches tall (EIA 3 RU) 14 inches deep max                            |

| <pre>front/rear panel material other panel material</pre> |   | aluminum steel, top and bottom vented                                                               |

## CONSTRUCTION

module plate material .... : aluminum

case color ...... : satin black

module plate color ..... : satin black

external component layout : as in diagrams below

Liquid crystal display shall be covered by transparent acrylic or equivalent material. PC board mount connectors shall be used for all back panel connections. These connectors shall also be mounted to the panel for additional strength.

panel artwork .....: single color silkscreen, white,

as in diagrams below

### MARKETING

target retail price ...: \$2000 for the base unit, including:

32 balanced/unbalanced line inputs

8 unbalanced line outputs

8 balanced line outputs

4 quad mixer modules

(8x16, 16x8, 32x4, 4x8x4 mixer modes)

additional modules  $\dots$ : 8 output balanced board (replace one existing)

8 output precision balanced board (replace one)

8 output unbalanced board (replace one)

quad mixer module to expand system

4 additional brings system to 16x16 and 32x8

12 additional brings system to 32x16

8 input equalizer board, 3-band

8 input equalizer board, 4-band (2-parametric)

DSP effects module

modules are installed internally and via back-panel brackets.

### 3.2.3 Panel Layout

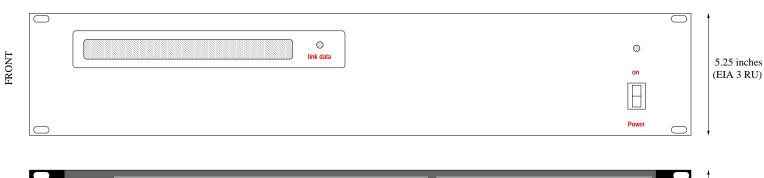

The panel layout for the mixer unit is shown in figure 8.

## 3.2.4 Concept Rendering

Figure 9 shows the original concept rendering of the mixer unit.

19 inches (EIA rack)

Figure 8: Mixer unit panel layout and silkscreen artwork.

Figure 9: Mixer unit concept rendering.

## 4 Module-Level Hardware Specifications

#### 4.1 Control Board

#### 4.1.1 System Description and Diagram

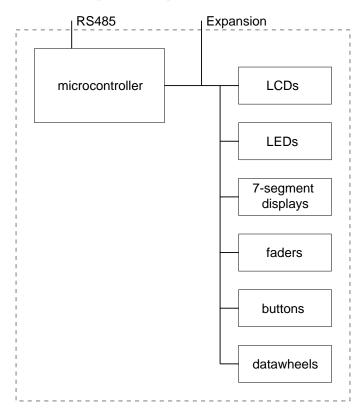

The control board is a simple piece of hardware, as it is mainly a variety of input and output devices connected to a microcontroller. Many types of output devices are used, ranging from simple LEDs to graphics-capable liquid crystal displays. Three main types of input devices are used: buttons, datawheels and faders.

Figure 10 shows the overall system diagram. This view depicts the system in terms of each of the input and output elements.

Figure 10: Control board, overall system diagram.

#### 4.1.2 Module Overview

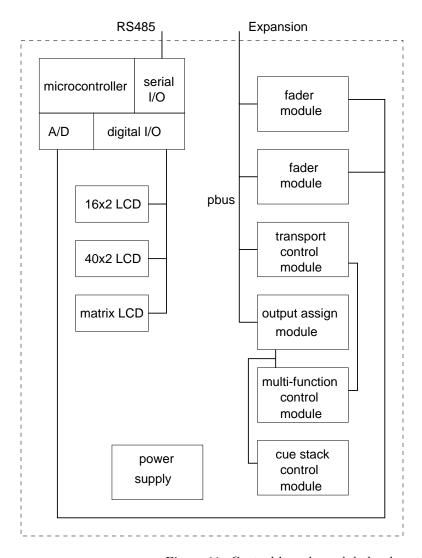

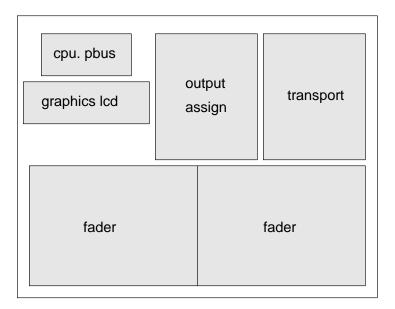

Figure 11 shows the various components of the control board, at the module level. The control board is designed in a modular fashion, such that larger models with dozens of faders, transport controls, etc. can be built. In addition, an expansion port provides the option to connect external add-ons, such as external fader boards and meter bridges.

Unfortunately, there is very little module duplication possible in this piece of hardware. The obvious options were to make one large module, or use the approach presented here. This design was chosen with an eye towards expandability as well as manufacturing cost. Manufacturing one large PC board costs a significant amount of money, whereas some money is saved by the duplication of the largest board, the fader module. It can be argued that the cost of the components required to connect all of the boards together is significant, but in general it seems a wise decision from an engineering standpoint to make smaller modules that can be combined into

Figure 11: Control board, module-level system diagram.

many different forms, not to mention debugged in a more sane fashion. This technique is often employed in lighting control boards, where different sized boards are built from small, modular building blocks.

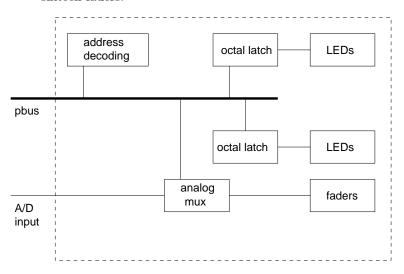

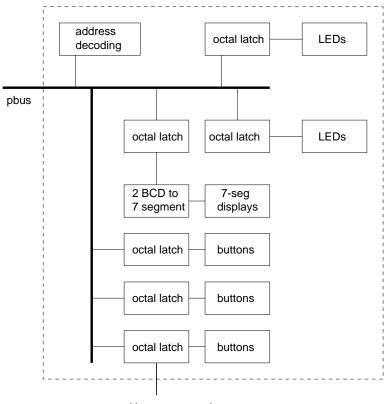

#### 4.1.3 Fader Module

Each fader module shall contain eight linear taper potentiometers, sixteen LEDs, and the necessary Pbus interface circuitry. Figure 12 shows the functional diagram of a fader module. The prototype of the control board shall contain two of these fader modules, providing a total of sixteen faders.

Figure 12: Control board, fader module diagram.

#### 4.1.4 Output Assignment Module

The output assignment module shall contain eighteen momentary buttons, two digits of 7-segment LED displays, sixteen LEDs, and the necessary Pbus interface circuitry. Additionally, it shall provide a means of interfacing the additional buttons of the cue and universal interface sections of the control board. Figure 13 shows the functional diagram of the output assign board.

#### 4.1.5 Transport Control Module

The transport control module shall contain 7 buttons, a datawheel, 3 LEDs, six digits of 7-segment displays, and necessary interface circuitry on a PC board. Additionally, a connection for the datawheel of the universal interface section shall be provided. Figure 14 shows the functional diagram of the transport control board.

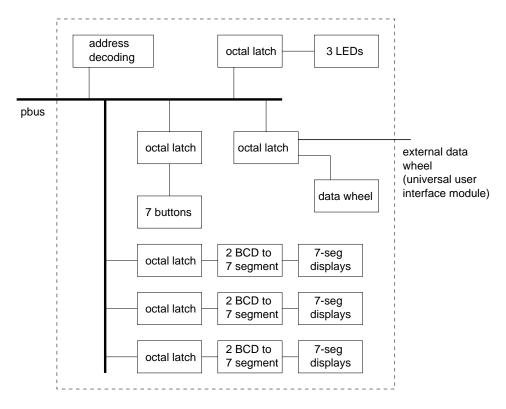

#### 4.1.6 Microcontroller Module

The microcontroller module used for in the control board shall be of sufficient computing capability to handle polling of all of the input hardware (buttons, faders, etc.), driving of the three LCD modules, and serial communication at 19.2Kbps.

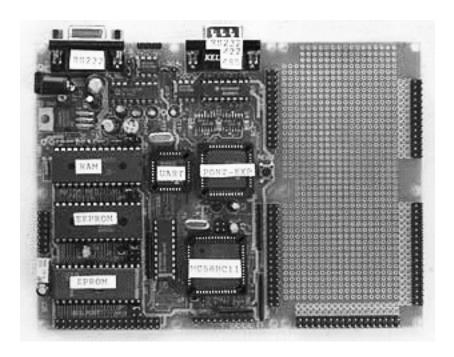

For the prototype, a pre-made Motorola 8MHz MC68HC11 microcontroller board will act as the embedded processor for the control board. This board contains an RS232 port, an 8-input A/D converter, an I/O port, address decoding logic, and contrast adjustment for liquid crystal displays. Figure 15 shows this microcontroller board.

external button connections (from universal user interface & cue modules)

Figure 13: Control board, output assignment module diagram.

Figure 14: Control board, transport module diagram.

Figure 15: Axiom CMM-11A8 single-board computer, used in the mixer unit.